时间:2023-06-11 10:19

人气:

作者:admin

以智能芯片为基石和核心,智能物联网设备需要融合数据的感知、存储、计算、决策等多种功能。在传统物联网系统中,传感器芯片、模数转换芯片、处理器芯片、存储器芯片等都是分立器件,这使得设计环节割裂,缺乏全局优化,难以克服系统的功耗和能效瓶颈。 低功耗物联网芯片技术通过将感知、存储、计算等处理过程融合,形成一体化的异构芯片架构,有效降低数据搬移的开销,减少无效数据的处理,从根本上突破整体系统能效瓶颈。在该研究领域,前沿的技术发展方向有低功耗数据感知技术、高能效 AI 硬件加速技术、低功耗芯片架构技术等。

低功耗数据感知技术旨在通过新型数据采集电路拓扑降低数据采集芯片功耗,提升数据感知精度,如从传统“电压域”数据转换转变为“电荷域”“时间域”等数据转换模式,从传统奈奎斯特转换转变为自适应采样转换等;高能效 AI 硬件加速技术旨在通过轻量级硬件加速器设计提升芯片计算能力,提升芯片计算能效,如从传统“冯·诺依曼架构”计算模式转变为“存内计算”的计算架构模式,减少数据传输损耗并提升芯片计算能力;低功耗芯片架构技术旨在通过新型芯片体系架构设计降低芯片功耗,尤其是长时间的待机功耗,如从传统“同步计算”体系架构转变为“异步事件驱动型”无时钟低功耗架构,通过匹配芯片的工作活跃度与实际事件行为来显著降低待机功耗。

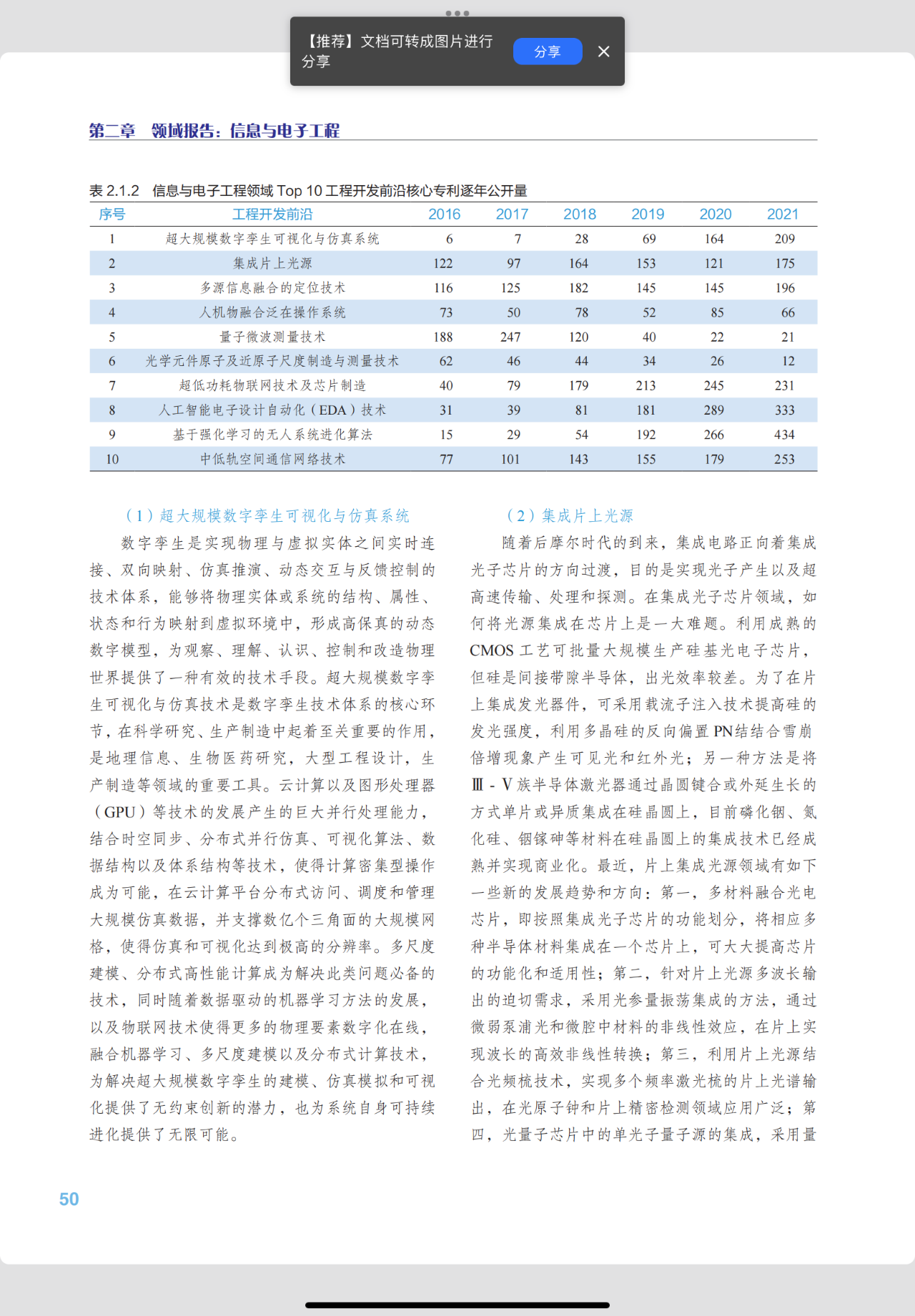

此外,前沿研究也在持续探索数据感知、计算、存储、传输的多环节协同创新,发展“感知 – 计算 – 存储 – 传输”一体化集成的高能效超低功耗物联网芯片。 该前沿核心专利公开情况见表2.1.1,核心专利2016—2021逐年公开情况见表 2.1.2。

叶乐,北京大学博雅特聘教授/博导,集成电路设计系副主任(主管科研),人工智能研究院双聘博导。杰青(22年)、优青(17年)和北京市科技新星(18年)。2010年获北大博士学位,之后进行博士后研究,2012年留校任教至今。主持十三五国家重点研发计划项目,基金委“后摩尔重大研究计划”集成(重大)项目等纵向项目,以及华为、华大九天、中兴通信等企业委托项目。主要从事超低功耗/高能效芯片、AIoT芯片、存算一体AI芯片、模拟与数模混合芯片等领域的研究。在ISSCC、JSSC、TCAS-I等国际权威期刊/会议上发表70余篇论文;尤其在“芯片奥林匹克”ISSCC上发表论文10篇,其中2篇为亮点论文,分别为ISSCC“前瞻芯片分会”和“模拟芯片分会”国内首次亮点论文;申请发明专利40余项,授权10余项。与英特尔芯片成果共同荣获ISSCC 2021最佳芯片展示奖,为国内首次获奖;荣获2021年度“中国半导体十大研究进展”等奖项。与集成电路产业界深入合作,部分成果获得转化应用。

编辑:黄飞