时间:2013-07-12 14:56

人气:

作者:admin

各国对LED灯泡的功率因数要求日趋严格,让LED驱动电路设计挑战与日俱增,因此半导体业者藉由改良降压拓扑结构,开发出可兼顾小体积、高能效与高功率因数要求的新一代LED驱动方案,有助开发人员设计出功率因数达0.9以上的LED灯泡。

随着白炽灯泡逐步被淘汰,节能萤光灯(CFL)和发光二极体(LED)将成为提供显著节能效果的两种照明选择。尽管CFL技术成熟,然白光LED发展快速,每颗LED元件的输出流明与光效已愈来愈高。LED灯泡的使用寿命是标准白炽灯泡二十五倍以上,且光效已超越CFL灯泡的性能水平。

大多数常见CFL灯泡中的电子安定器为电容型,典型功率因数(PF)为0.5~0.6。这表示虽然住户仅为灯泡所标示的功率付款,但电力公司实际上必须产生成比例的伏-安(Volt-amp)电量,故功率因数为0.5的13瓦CFL灯泡,代表的是26伏-安的负载,只略低于60瓦白炽灯泡伏-安数的 50%。

也因此,美国能源之星(Energy Star)规定功率大于5瓦的LED灯泡最低功率因数须为0.7,而诸如嵌灯及聚光灯等商用LED灯具的最低功率因数须达0.9。放眼全球,美国对LED灯泡的功率因数要求并非最为严格;最严格的当属韩国,该国要求所有输入功率超过5瓦的灯光的最低功率因数须达0.9,此要求将为设计LED驱动电路的设计人员带来挑战,他们必须综合评估能效、可用空间及整体物料清单(BOM)成本,以提供优化LED照明方案。

导入降压拓扑结构电路 LED灯泡PF大跃进

白炽灯泡只为某个特定线路的电压而设计;但设计师不须要考虑如何使一个通用设计的LED灯泡风行全球。此外,LED灯泡内的电源不须要与负载电气隔离,因其整合在单个壳体(Housing)中;但仍须注意机构的设计,必须以物理方法符合安全要求。考虑到这点,设计人员就不再须要倚赖隔离返驰拓扑结构,做为唯一的电源转换架构选择。

在特定边界条件下,可以优化降压拓扑结构来提供良好的功率因数。要提供高功率因数,输入电流要与线路一致,且随着整流线路电压增加而正比例地增长。降压拓扑结构的缺点是输入电压Vin大于输出电压Vout后,才有电流流动,因此LED串电压与线路电压相比必须较低。在大多数情况下,这不成问题,因为与线路电压相比,串联LED的数量相对较少,如八颗串联LED的总电压约为25伏特,不到整流120伏特AC输入峰值电压的15%。

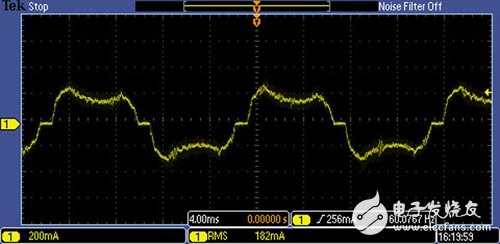

高功率因数升压转换器的一种控制方法是固定导通时间控制,这种控制模式下,电感、电流到达零时,将重新开始一个开关周期。为了控制功率,设计人员须使用回馈来调节导通时间,并可运用相同的概念来实现降压拓扑结构。于固定导通时间情况下,流过电感/开关的电流与线路以正比例上升,从而提供接近完美的功率因数,其中的折衷是开关周期顶部的峰值电流可能极大。灯泡应用中并不要求极佳的功率因数;因此,如果开关周期中的某一部分峰值电流被限制,就可以降低开关及电感的损耗,提供更高的转换能效并限制电感尺寸。这方法产生的典型线路电流波形并不能如图1所示那样极贴近正弦曲线。然而,这方法产生的波形轻易地提供大于0.9的功率因数,但折衷则是失真增加。

图1 输入电流波形

提升灯泡PF LED控制器扮要角

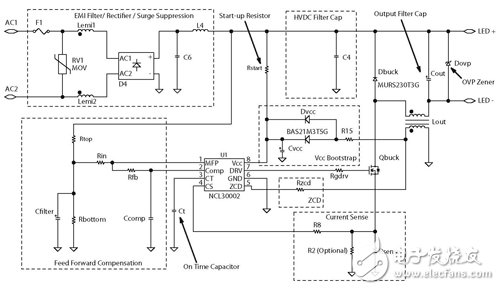

为了应用这种固定导通时间/峰值电流混合机制,半导体业者开发出NCL30002控制器(图2)。

图2 功率因数校正降压应用电路图

由该控制器电路图可观察到LED参照高压轨;而电源开关则参照地面,此称为反向降压。其可简化架构,主因系可直接感测峰值LED电流,并驱动单结型场效应电晶体(FET),毋须使用位准转换器。