时间:2023-06-27 11:43

人气:

作者:admin

静态时序分析(Static Timing Analysis, 以下统一简称 STA )是验证数字集成电路时序是否合格的一种方法,其中需要进行大量的数字计算,需要依靠工具进行,但是我们必须了解其中的原理。

在综合工具(DC/Genus 等),布局布线工具(ICC2/Innovus 等),时序分析工具(PrimeTime/Tempus 等)中都嵌入了不同的STA引擎,这些引擎往往在时间和精度方面有一些折衷,但是目的就是以尽量小的误差去模拟物理器件和绕线的SPICE模型,从而更接近芯片生产出来后真实的性能。

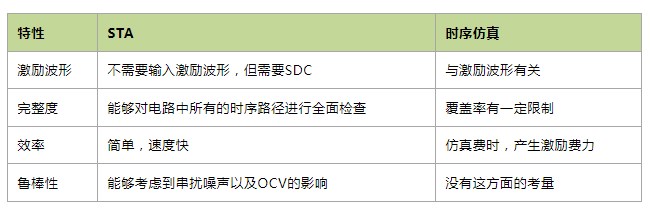

为了更好地理解STA,有必要提一下时序仿真,它是另外一种验证数字集成电路时序是否合格的方法。下面用一张表来对比一下这两者之间的区别:

既然,STA在数字集成电路中如此不可或缺,那具体是由哪些人负责,又是做什么具体的工作呢?关于这个问题,在不同的公司各有不同,但是负责STA的人一般都会同时负责综合,生成SDC,标准单元工艺库的选择,时序签核(Timing Signoff)及相关标准的制定等等。他们需要对设计有一定了解,更加需要对工艺的时序特性有全面地掌握,在系统性能指标的定义时需要提供参考意见。作为芯片时序性能检查的最后的把关人,需要一定经验的积累,同时也需要敏锐发现并解决潜在新问题的能力。

当然,STA也有它的局限性,需要通过仿真进行交叉验证。下面简单列举几个方面: