时间:2024-03-19 12:26

人气:

作者:admin

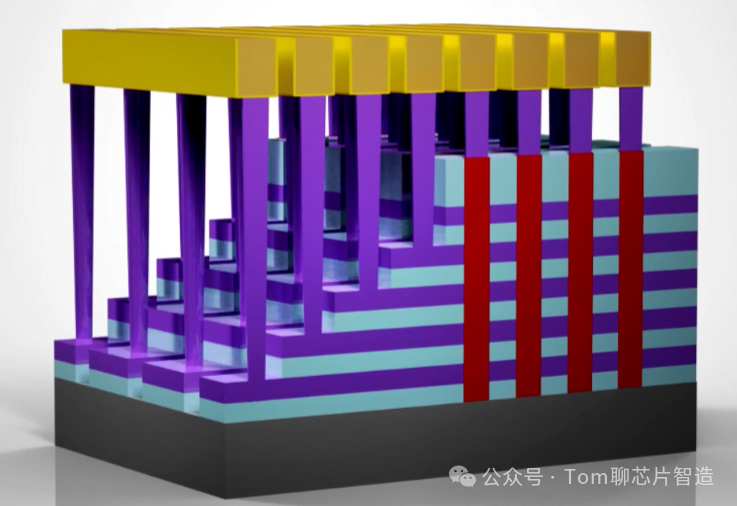

3D NAND绝对是芯片制程的天花板,三星,海力士,英特尔,长江存储等都有3D NAND的产线,代表了一个国家的芯片制造水平。今天,我们就来剖析一下3D NAND的主要制作流程。

1,基底准备:选择12寸特定晶向的硅片。

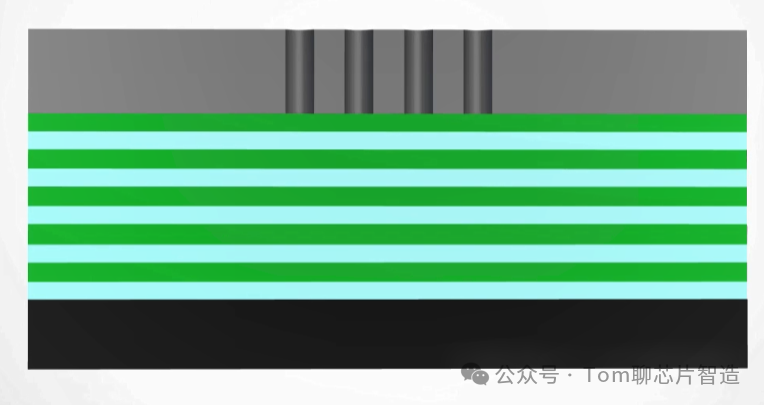

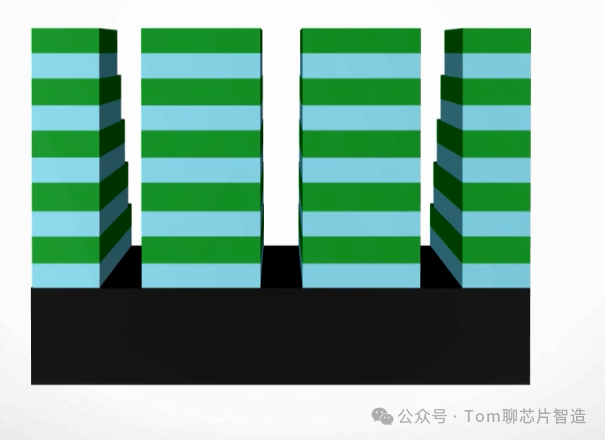

2,SiO2与SiNx交替镀膜,每层膜层在几十纳米左右。根据产品的不同,膜层的层数也不同。图中只是示意图,只有几层。但实际有64,128,400层等层数。

3,沉积无定形硅碳膜,这个是用来做沟道刻蚀的硬掩模。

4,硬掩模刻蚀,将硬掩模开口,以便于刻蚀堆叠的SiO2与SiNx材料

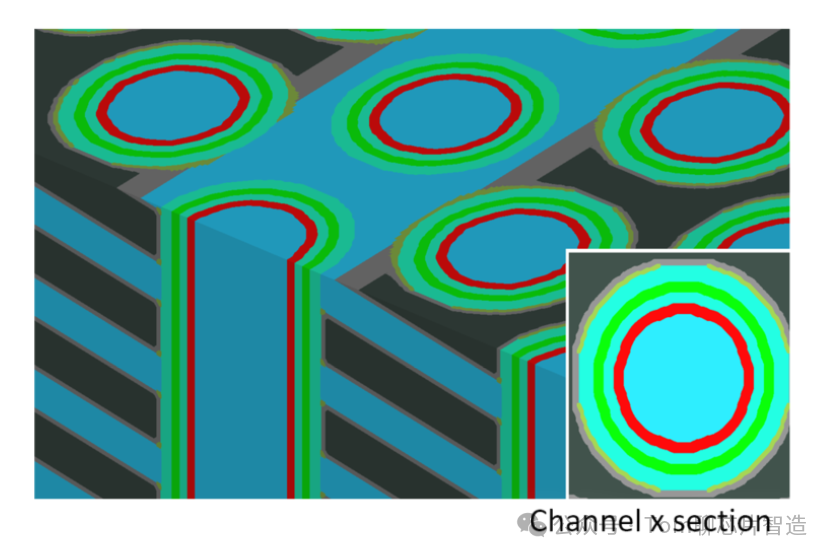

5,沟道通孔刻蚀,见文章:

《 3D NAND的沟道通孔是怎么做出来的?》

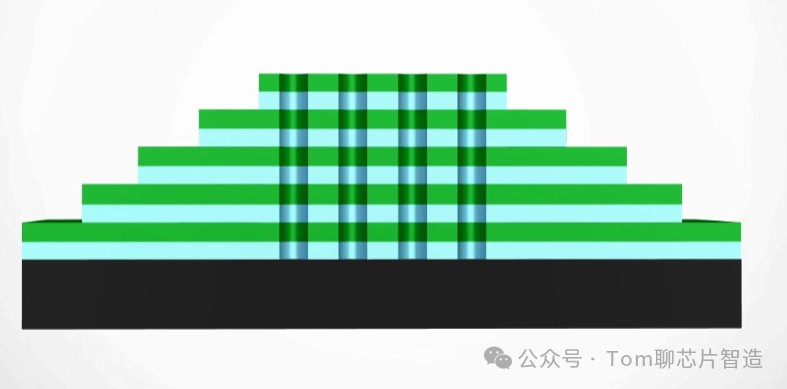

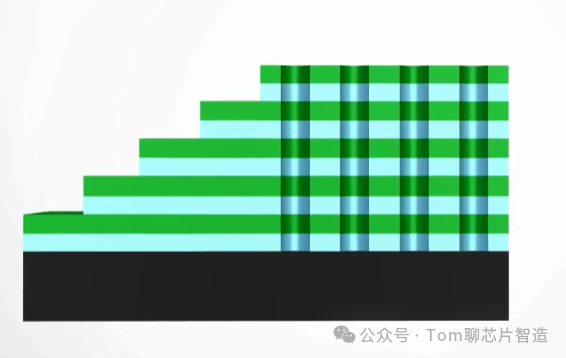

6,台阶刻蚀,见文章:

《3D NAND的台阶蚀刻(刻蚀)》

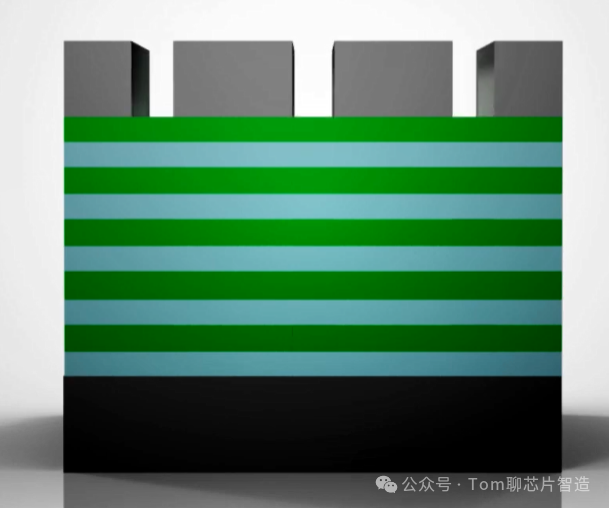

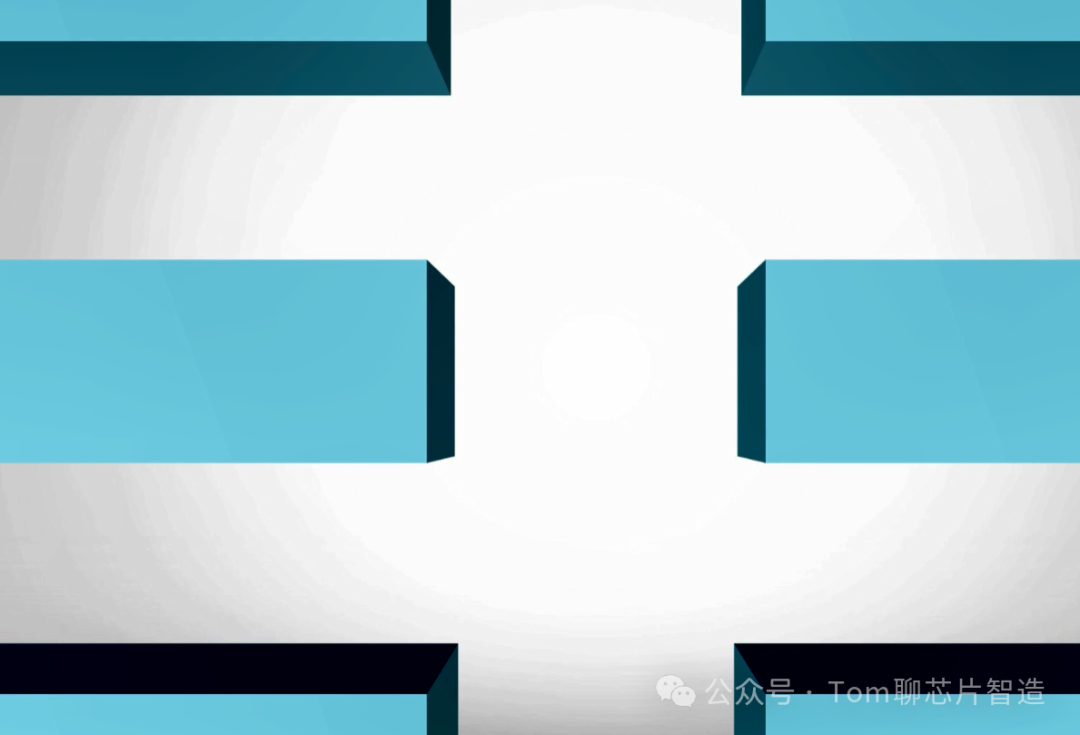

7,沉积无定形硅硬掩模,图片为侧视图

8,将硬掩模开孔

9,slit etch:将SiO2与SiNx的堆叠层刻蚀为一个个沟槽,

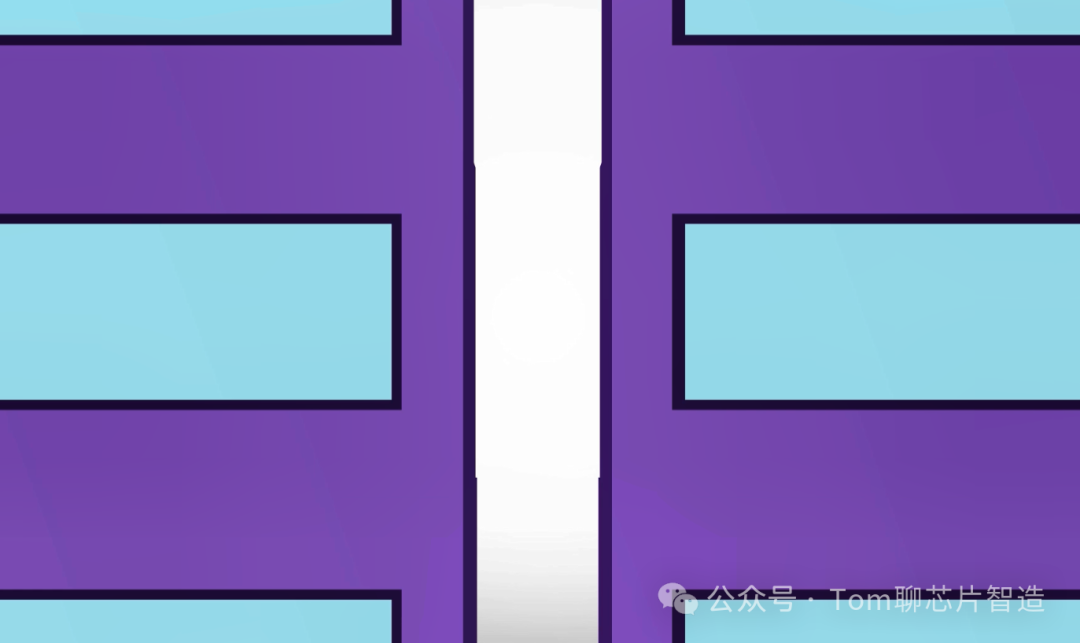

10,将堆叠层中的SiNx刻蚀掉,填充TiN,钨(W)等,即word line fill工艺。

11,刻蚀掉多余的钨,之后需要对沟道通孔进行填充,因此需依次沉积阻挡氧化层,Charge Trap SiN (电荷陷阱氮化硅),Tunnel Oxide (隧道氧化物),Poly Si (多晶硅),Core SiO2 (硅基体)。功能区主体结构完成。

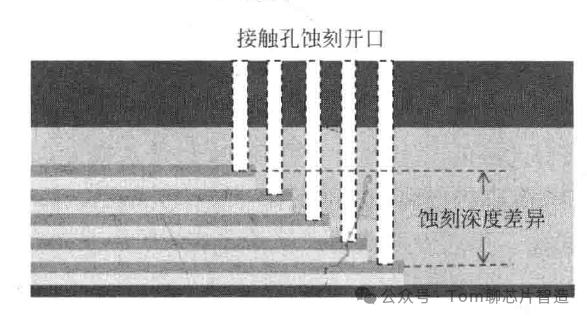

12,沉积介质层,并用CCP-RIE进行接触孔蚀刻。

13,用金属填充接触孔,并制作出连接接触孔的金属导线-Bit line,3D NAND的整个制程结束。

文中精简了比较多的重复步骤,实际工艺在数百步以上。

审核编辑:黄飞