时间:2023-08-25 09:53

人气:

作者:admin

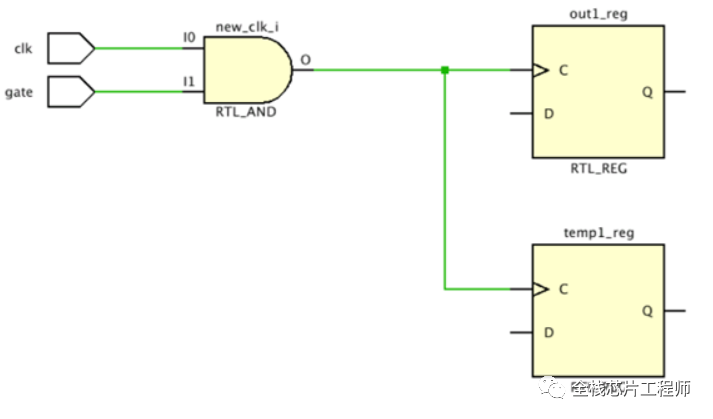

首先,ASIC芯片的clock gating绝对不能采用下面结构,原因是会产生时钟毛刺,之前发文说过,此处不再赘述,那么下面这结构在FPGA里面实现是什么结果呢?

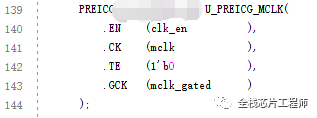

芯片ASIC设计中,不可避免会例化门级单元,比如CRG里:

【解决办法1】将代码中的gating cell去掉,或者用ifdef方式定义FPGA的代码

将代码中的gating cell去掉的话,工作量太大,并且代码freeze之后不允许修改代码。

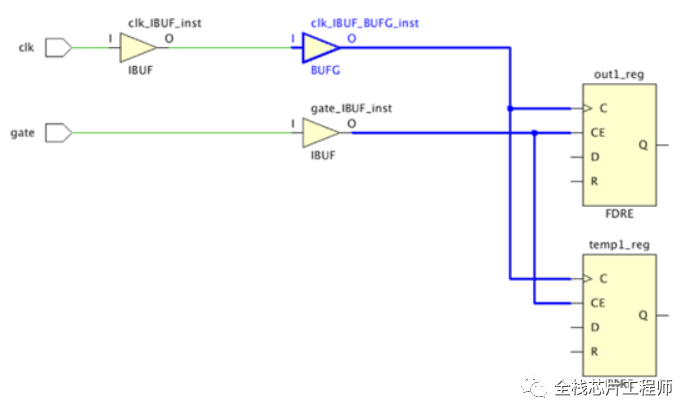

【解决办法2】:让Vivado综合工具将clock gating cell转换为时钟直通,也就是时钟直接连接到寄存器的CK端,门控信号连接到寄存器的CE(clock enable)端口。

审核编辑:刘清