时间:2023-06-26 14:58

人气:

作者:admin

FPGA开发过程中软件的综合布线耗时很长,这块对FPGA产品开发的进度影响很大。

伪路径表示该路径实际存在,但该路径的电路功能无须考虑时序约束。

通过定义伪路径,通知vivado等FPGA开发软件无需对这些路径进行时序优化布线。

这样FPGA开发软件就会自动跳过这部分路径的优化,可以减少综合布线的优化时间。

使用伪路径命令可以有效地减少时序分析的复杂度,同时提高系统性能和可靠性。

伪路径主要应用于异步时钟或异步复位的情况下,例如:

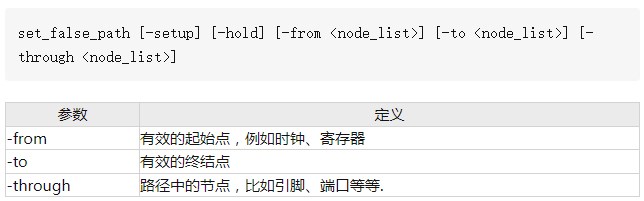

伪路径约束语法为:

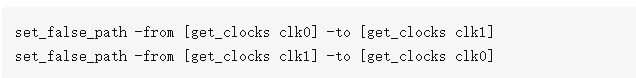

这里需要注意:伪路径约束是单向的,不是双向的,如果两个时钟域相互之间都有数据传输,则需要对两个方向的都做时序约束,如下所示:

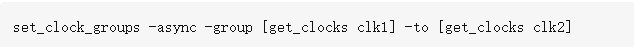

或者这样写也是可以的:

默认情况下FPGA开发软件默认每条路径都是单周期路径,即从上一个寄存器到下一个寄存器的时间默认为一个周期内可达,并按照这个约定去布线优化。

其实我们写的代码基本默认就是单周期的,时序达不到就拆分代码逻辑,拆分成多个周期完成即可,则不需要做多周期路径约束。

但有时也存在需要多周期路径,设定这个路径从起点到终点需要1个周期以上才能到达,这时就要进行多周期约束,但这部分约束也用的少。

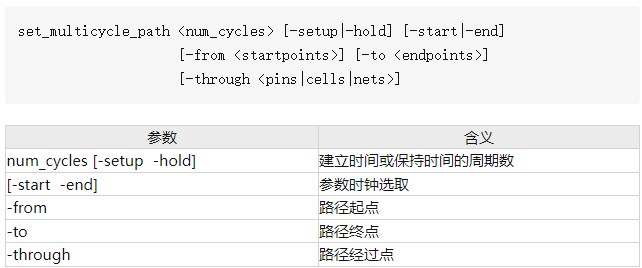

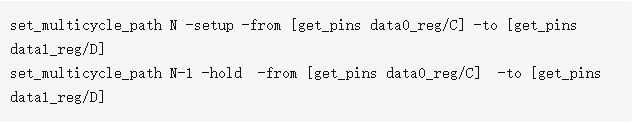

多周期约束语法:

单时钟域下,数据经过N个周期从起点寄存器到达终点,约束如下:

本文介绍了伪路径和多周期路径的使用,但要注意的是伪路径约束不能滥用,只能用在一些异步时钟或异步复位这些对于时序要求不高的路径,对于关键路径,不能用这个约束命令,还是要从HDL代码来优化。

上一篇:FPGA时序约束的原理是什么?

下一篇:12英寸硅晶圆可能过剩