时间:2011-07-04 11:04

人气:

作者:admin

摘要:提出了一种基于SOPC技术的数据采集和存储系统的解决方案。该系统通过在一片Xilinx公司Spartan 3E系列的FPGA芯片上配置micro-blaze软核处理器、用户自定义的数据采集与存储接口逻辑、USB传榆模块和总线接口模块来实现其硬件电路。该数据采集系统可同时对多种信号进行测量,有较大的存储容量。由于采用了SOPC技术,该系统具有设计灵活、集成度高,以及较小的体积和较低的功耗等优点。

引言:随着集成电路的不断发展,可编程逻辑器件FPGA因其功能强大,设计灵活,开发周期短等特点,得到越来越广泛的应用。于是片上可编程系统(System On Programmable Chip,SOPC)的设计方法也越来越受到重视。SOPC将微处理器、存储器、定时器、通用I/O接口等系统设计必需的功能模块以及用户设计的有特定功能的模块集成到一片可编程逻辑器件上,构建一个具备软,硬件在系统可编程功能的可编程片上系统。这种非常灵活的电路设计方式使得对整个电路系统的裁减、扩充、升级变的很容易。这样可以缩短电路设计的开发周期,节省开发成本。

1 系统总体结构

整个系统由xilinx公司的spartan3E高性能、低成本的90nm FPGA和一些外围电路组成。主要有AD转换器、FLASH存储器、系统PROM配置电路和电源模块等,其系统总体结构如图1所示。

系统核心采用嵌入式技术,在一片芯片上实现,它包含Xilinx公司的一些标准总线IP核如中断控制器,通用输入输出端口等模块和带有PLB总线接口的用户自定义的数据采集与存储IP核。其中用户自定义的IP核是用VHDL语言设计的,它包含AD控制逻辑、FLASH控制逻辑、DMA传输控制逻辑和FIFO缓存模块等。

整个系统设计可以分为硬件设计和软件设计两个部分。利用SOPC技术结合VHDL硬件描述语言,在芯片内部设计硬件控制系统;利用EDK(嵌入式开发套件)为特定硬件配置自动生成的软件包结合C语言,设计基于Microblaze处理器的软件控制程序。

2 系统结构

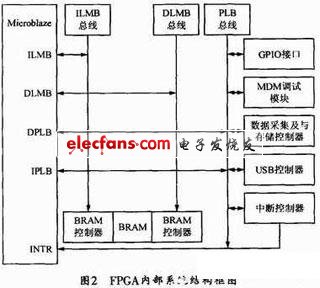

FPGA的硬件设计先确定要用的外部接口,然后进行IP核设计,将IP核的逻辑功能映射到FPGA芯片上。其系统结构框图如图2所示。

2.1 AD转换芯片

AD转换器采用MAXIM公司的MAXIM1308芯片,它是12位模数转换器(ADC)提供8个独立输入通道,独立的采样保持(T/H)电路为每个通道提供同时采样,提供+5V输入范围,20MHz、12位双向并行数据总线用来提供转换结果,并可接受数字输入来单独配置每一通道的开启和关闭。

2.2 FLASH存储器

FLASH存储器芯片采用8片三星公司的K9XXG08UXA系列的NAND Flash存储器,该存储器是按页进行读写按块擦除,通过I/O管脚分时复用发送命令/地址/数据。每片的存储容量为512MB。存储过程使用流水线方式对数据进行存储。

上一篇:图解国内物联网发展目标

下一篇:CPLD系统上的信号发生器设计