时间:2009-03-04 11:38

人气:

作者:admin

AS1773协议

AS1773由美国汽车工程师协会制订,是MIL-STD-1773的增强版[1],现已被广泛应用于航空、航天及工业控制等各个领域。该标准协议处理部分与MIL-STD-1773几乎完全一样。仅仅在传输速率上改为20 Mbps,在状态字/命令字前面增加了前导码。因此,AS1773和MIL-STD-1773两种总线终端可采用相同的协议处理部分来实现。

AS1773协议简介

1773总线上一共有总线控制器(Bus Controller, BC)、远程终端(Remote Terminal, RT)和总线监视器(Bus Monitor, BM)三种类型的终端。这三种终端都连接到总线上从而形成广播信道。每个终端通常同时连接到多条总线上,并从中选择一条总线用作平时通信的主总线,而其他总线则作为空闲的冗余总线,一旦主总线发生故障所有终端就切换到冗余总线继续进行通信。所有终端在总线上以20 Mb/s的速度传送信息,总线上最多能连接32个终端[2]。

突发同步

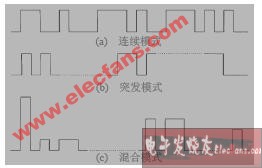

一般来讲,数据通信中通常包括三种形式的数据格式,如图1所示。第一种是连续模式,数据连续发送,而且“1”和“0”的比例接近平衡,两个逻辑变化之间的间隔是严格固定的,例如在点到点通信中的4B5B线路码等。第二种是突发模式,“1”和“0”的比例以及两个逻辑变化之间的间隔是没有严格的限制的,例如串行通信的RS-232接口。第三种是报模式和突发模式的混合模式,不同的报的幅度值可能是不同的,并且,不同的报之间有一个保护时间。这种类型的数据通常出现在报文传输的通信中,如以太网等。对于突发同步来说,就是要对接收的突发数据进行同步

[2]。通过对异步传输模式—无源光网络(Asynchronous Transfer Moder-Passive Optical Network, ATM-PON)的研究,可以发现ATM-PON的突发同步和1773协议突发同步比较类似,仅在前导的格式要求方面有一点区别。ATM-PON的前导包括前导码、防护时间、功率恢复BYTE、突发同步关键字、BYTE 同步关键字等;1773的前导为16 b的“1”。因此可以在研究ATM-PON的基础上,对其进行适当的修改,来满足1773协议的突发同步要求。对于ATM-PON的突发同步,目前主要有模拟、门控振荡、多相时钟三种方法对突发数据进行同步处理。下面对这三种方法分别进行说明。

图1 数据格式

图1 数据格式

模拟

本地时钟信号和数据信号经过限幅后进行积分,其中数据信号分为两路积分,一路为高电平,一路为低电平。时钟和数据经过积分后的信号送入比较器,由跟踪采样电路对比较器输出的差值进行采样,采样值用于控制压控移相器,使输入信号得到合适的延时,完成同步过程。

2.2 门控振荡

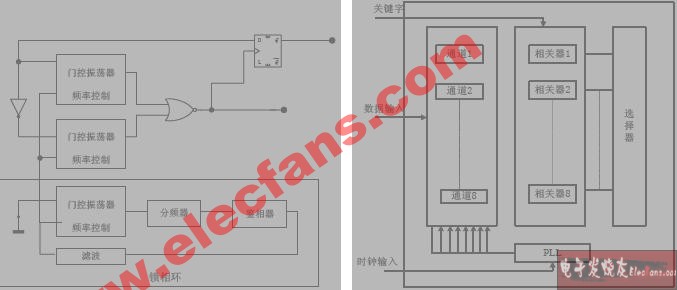

这种方法的原理图如图2所示。振荡系统包括3个振荡器。A、B用于同步输入信号,C用于控制A,B。A,B输出的方波频率要和输入频率一致。每一个振荡器随信号变化开启或关断,从而和输入信号达到同步。如果振荡器输出频率和输入信号频率一致的话,即使信号有长的连“0”或连“1”也可以保持同步。为了使A,B振荡器达到一致。可以采用自动调谐的方式,引入1个主振C,使其连续运转,并用锁相环使它与外部固定参考频率保持一致。频率校制信号由两个从振共享.从而使输出时钟达到理想要求[3]。这种无记忆系统有一个非常重要的持性,那就是在门控振荡器关闭时,任何由于振荡颠串或传输速率不匹配而积累的相位错误都会被去掉。这种方法对工艺的水平要求较高,并且不利于修改,成本也较高。对于速率较低的系统来说,用这种方法性价比不高。

图2 门控振荡原理框图 图3 多相时钟系统框图

2.3 多相时钟

传统的突发同步器中,主要包括多相时钟和相位校准器、相关器及选择器。图3为基于多相时钟的突发同步原理图。由多相时钟发生器产生多相时钟,多相时钟的最大相位差为360°。同时根据每路时钟相位与主时钟相位的关系,分别加入一定的延时,使抽样后的每路数据都与主时钟同步。抽样后的数据进入相关器,相关器把抽样的数据与关键字比较的结果传给选择器,选择器根据每路数据的相关结果选出其中与关键字最为相关的那一路数据,输出恢复后的数据和时钟,从而达到突发同步的目的[4]。这种方法开发成本低、周期短,对于速率不是很高的系统,是一种理想的突发同步方式,但对速率比较高的系统,对现场可编程门阵列(Field Programmable Gate Array, FPGA)的要求相当的高,比较难于实现。

设计实现

3.1 设计原理

本文设计模块由多相位时钟产生电路、多路采样电路、相位调整电路、判别搜索电路、开关及输出电路等组成。多相位时钟产生电路根据输入的本地时钟Clk0 产生相位间隔90°并与OLT同频的4个时钟信号,然后将这4个时钟信号( Clk0、Clk1、Clk2、Clk3) 送到多路采样电路。多路采样电路用这4个时钟信号对突发输入的串行数据进行采样,得到4路相位各异的数据,分别送到相位调整电路。相位调整电路将这四路相位各异的数据调整到Clk0 相位上,分别送到判别搜索电路及开关电路。判别搜索电路在规定的时间内对4路数据码流的前导码进行搜索,当在相邻的3个数据流中检测到“101”时,便产生控制信号送至开关电路,以控制开关电路选用中间相位的数据作为所恢复的数据。输出电路负责输出被选中的数据和相应的Clk0 时钟。

3.2 具体实现

本文通过多相时钟的方法进行突发同步的实现,采用Altera公司的Cyclone EP1C6Q24C08的FPGA来实现突发同步电路。如图4所示,40 MHz主时钟信号,通过FPGA内部的锁相环形成4个相位相差90°的多相时钟信号。分别对输入数据进行抽样,把四路抽样数据进行相位调整,使其相位都调整到Clk0。然后搜索电路,对抽样数据进行“101”的搜索,看那一路时钟先得到“101”,然后选择中间的一路数据进行输出。即如果Clk0先采到数据,就把Clk2抽样的数据作为恢复数据输出;如果Clk1先采到数据就把Clk3抽样的数据作为恢复数据输出;如果Clk2先采到数据就把Clk0抽样的数据作为恢复数据输出;如果Clk3先采到数据就把Clk1抽样的数据作为恢复数据输出。搜索电路确定了最佳数据作为恢复数据后,便产生控制信号送至选择输出电路,输出电路把保存在寄存器的采样数据通过串行输出最佳采样的数据及时钟。

基于AS1773协议的突发同步设计