FDLs设计

由于技术条件的制约,全光缓存的实现有较大的难度。目前光缓存只能运用光延迟线组,即一组不同长度的光纤实现。文献[1]提出了三种不同的FDLs设计,如图2所示。

|

|

(a) FDLs设计方案1 (b) FDLs设计方案2 (c) FDLs设计方案3

图2 FDLs设计方案

图2a中,FDL缓存由N个延迟线构成,每个延迟线提供不同的延迟时间,但每个延迟线提供的延迟是固定的,延迟范围为0到最大缓存时间B=(N-1)b,b为单个延迟单元(图中表示为一个圈)的延迟时间,N为FDLs的级数。

图2b所示的FDL缓存也有N个延迟线,但与图2a不同的是每个延迟线提供的延迟时间不固定,在0~B之间可变,其中B=(N-1)b=(20+21+,…,+2n)b。图中矩形框表示的是2:2的交叉单元,这种结构称为“可变延迟的”FDL缓存。固定延迟的FDL缓存实现较简单,但应用不够灵活;可变延迟的FDL缓存代价较大(主要与2:2的交叉单元数目成正比)。

图2c所示的结构是上述两种结构的混合结构。每个延迟线都提供可变的延迟,但延迟的范围各不相同,下限都为0,上限分别为b,2b,…,(N-1)b。

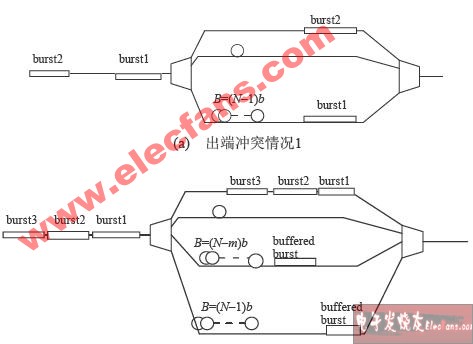

如图3所示,FDLs由于自身设计的局限性,会出现出端冲突问题。

图3a所示是两个突发数据包在同一条波长上先后到来,通过FDLs时,由于各自的时延不同,它们在FDLs的出口处产生了冲突。图3b所示是到达的突发数据包与已经缓存在FDLs中的突发数据包冲突,此冲突的存在会对节点的交换性能产生一定的影响。

(b) 出端冲突情况2

图3 FDLs出端冲突

OBS交换结构中FDLs和TWC的研究 |