时间:2018-03-23 10:05

人气:

作者:admin

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号与时钟做等长。数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。那么,时钟信号和地址同时到达接收端,波形的对应关系是什么样的呢?我们通过仿真来看一下具体波形。

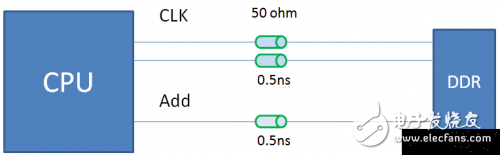

建立如下通道,分别模拟DDR3的地址信号与时钟信号。

图1 地址/时钟仿真示意图

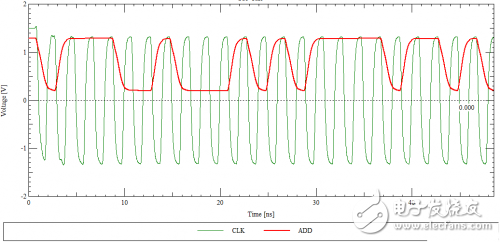

为方便计算,我们假设DDR的时钟频率为500MHz,这样对应的地址信号的速率就应该是500Mbps,这里大家应该明白,虽然DDR是双倍速率,但对于地址/控制信号来说,依然是单倍速率的。下面来看看波形,在地址与时钟完全等长的情况下,地址与数据端的接收波形如下图2,红色代表地址信号,绿色代表时钟信号。

图2 时钟信号与地址信号波形

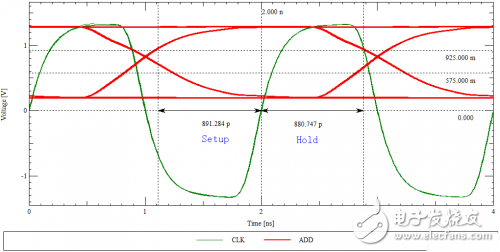

上面的波形我们似乎看不出时钟与地址之间的时序关系是什么样的,我们把它放在一个眼图中,时序关系就很明确了。这里粗略的计算下建立时间与保持时间。如下图

图3 时钟信号与地址信号波形

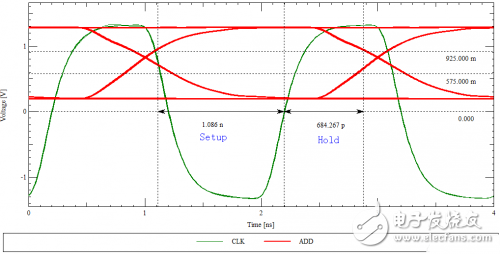

由上图3.我们可以知道,该地址信号的建立时间大约为891ps,保持时间为881ps。这是在时钟与地址信号完全等长情况下的波形。如果地址与时钟不等长,信号又是什么样的呢?仿真中,我们让地址线比时钟线慢200ps,得到的与眼图如下:

图4 时钟信号与地址信号波形