时间:2011-06-09 10:05

人气:

作者:admin

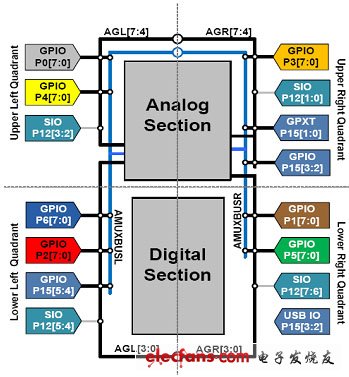

PSoC3内部可以分为模拟和数字两部分,模拟部分包括Delta-Sigma ADC、运算放大器、比较器、DAC和SC/CT模块。数字部分包括如CPU、RAM、ROM、DMA、UDBs、时钟等等。

模拟全局总线(AGs)和模拟多路复用总线(AMUXBUS)提供GPIO与内部模拟模块之间的连接,如图1所示,PSoC3一共有16根AGs分别分布于4个象限,每个象限包括4根AGs总线(AGR[7:4], AGR[3:0], AGL[7:4], 和AGL[3:0]);AMUXBUS可用于任何GPIO和大部分模拟模块输入输出之间的连接。这样,AGs和AMUXBUS可在GPIO和模拟模块之间提供高达18路的信号连接。

对于内部模拟模块之间的互连,PSoC3采用模拟局部总线(ABUS)来完成,ABUS总线一共8根,其中4根ABUSL[3:0]位于芯片左边,4根ABUSR[3:0]位于芯片右边。

另外在GPIO和模拟模块之间还有大约20路的专用通道,这些专用通道可提供低阻抗连接,比如在PSoC3中的IDAC和运算放大器Opamp,后面第3部分专门介绍。

图1,PSoC3 内部模拟/数字部分分布

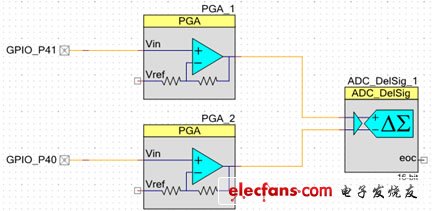

2,PSoC3模拟布线事例

Cypress提供的软件工具PSoC Creator可为用户提供模拟布线,当然用户也可以自己手动布线模拟器件以选择更好的管脚和更优的走线,下面以一个设计事例来说明。

若需要信号从P4[0]和P4[1]输入,经PGA1和PGA2放大,然后接入ADC的差分输入以采集信号,其在PSoC Creator中设计的原理图如下图2所示: