时间:2024-03-11 10:19

人气:

作者:admin

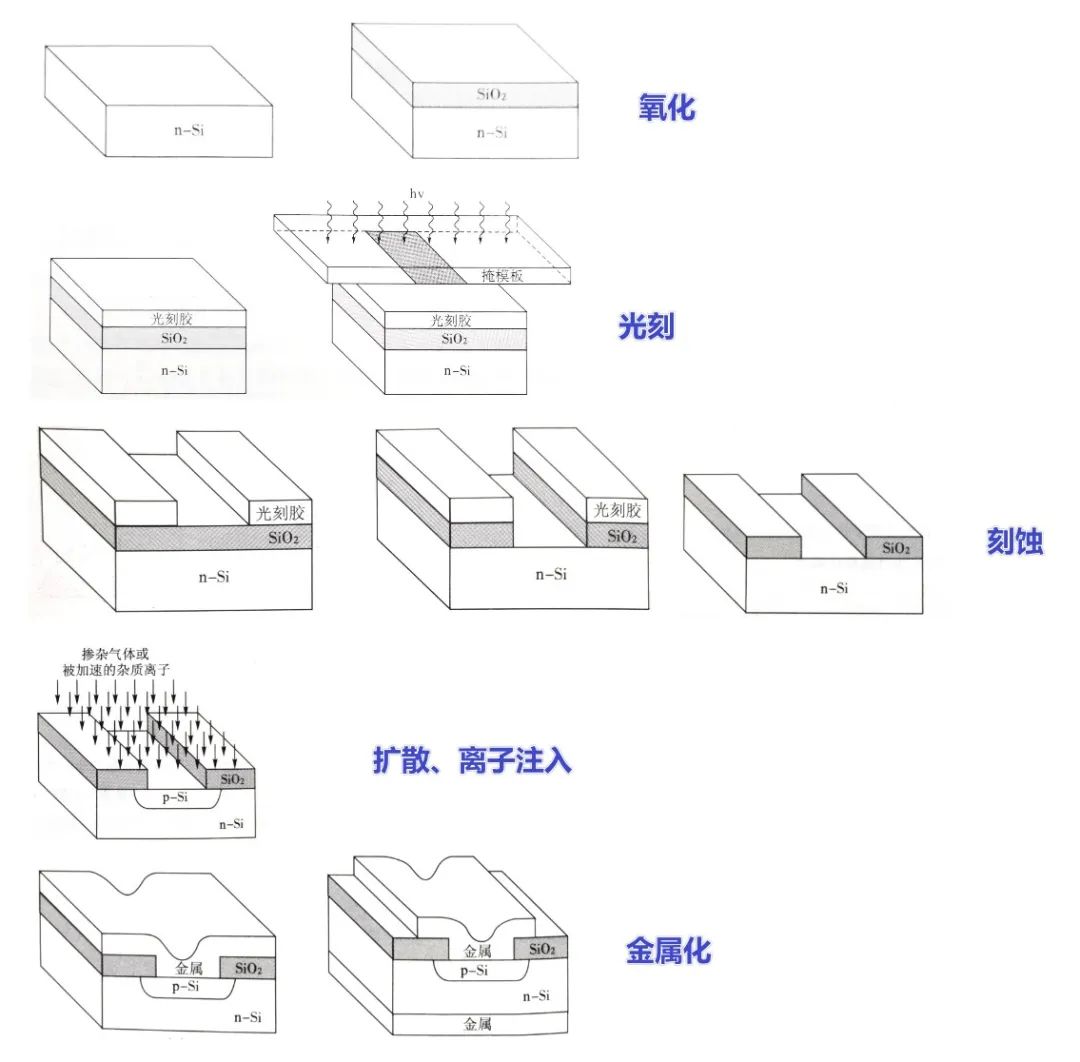

集成电路的平面工艺,主要包括氧化、光刻、刻蚀、扩散、离子注入和金属镀膜等。

一、氧化

一般来说SiO2是作为大部分器件结构中的绝缘体 或 在器件制作过程中作为扩散或离子注入的阻挡层。

氧化的方法有两种:

(1)湿氧氧化:氧化剂是氧气和水蒸气的混合物、氧化速度快:适合生长厚的氧化层(2)干氧氧化:可获得良好的Si-SiO2 界面。适合生长器件的氧化物薄层。

二、光刻和刻蚀

光刻技术可用于界定PN结的几何形状。

图1 (a)n型硅晶圆原材料;(b)干氧或湿氧氧化工艺处理后的晶圆;(c)涂敷光刻胶;(d)光刻胶通过掩模板曝光

step 2.1 形成SiO2层以后,使用高速旋转机在晶圆表面旋涂一层对紫外线敏感的光敏材料薄层(光刻胶)。之后将晶圆放在温度为80~100℃的环境下烘焙,目的是去除光刻胶中的溶剂,提高光刻胶的黏附力。

step 2.2 使用紫外线光源,通过具有某种图案的掩模板对涂有光刻胶的晶圆进行曝光,如图1(d)所示。根据光刻胶的类型,在晶圆表面光刻胶涂层的曝光区域将发生相应的化学反应,暴露在光线下的光刻胶涂层将发生聚合反应而难以被刻蚀。聚合物区域在晶圆放进显影剂后依然存在,而未被曝光的区域(在不透光的掩模板区域下)会溶解并被清洗掉。

step 2.3 图2.(a)显示了显影后的晶圆。将晶圆再次放在120~180℃的环境下烘焙20 min,以增强对衬底的黏附力,提高在即将进行的刻蚀工艺处理中的抗腐蚀能力。然后使用氢氟酸(HF)作为酸刻蚀液,除去没有被光刻胶保护的SiO2表面,如图2.(b)所示。

step 2.4 最后使用化学溶剂或等离子体氧化系统剥去光刻胶,如图2.(c)所示。此时,晶圆已完成了准备工作,可以进行后续的扩散或离子注入以形成pn结。

图2 (a)显影后的晶圆;(b)SiO2去除后的晶圆;(c)光刻工艺处理后的晶圆;(d)扩散或离子注入形成pn结;

三、扩散和离子注入

在扩散工艺中,没有被SiO2保护的半导体表面暴露在相反类型的高浓度杂质中,杂质以固态扩散的方式进入半导体晶格中。在离子注入工艺中,掺杂离子被加速以获得较高的能量,然后注入半导体内部。此时,SiO2层作为杂质扩散或离子注入的阻挡层。随后pn结形成,如图2(d)所示。由于掺入杂质的横向扩散,重掺杂区域要比光刻所开的窗口面积略微大些。

四、金属化

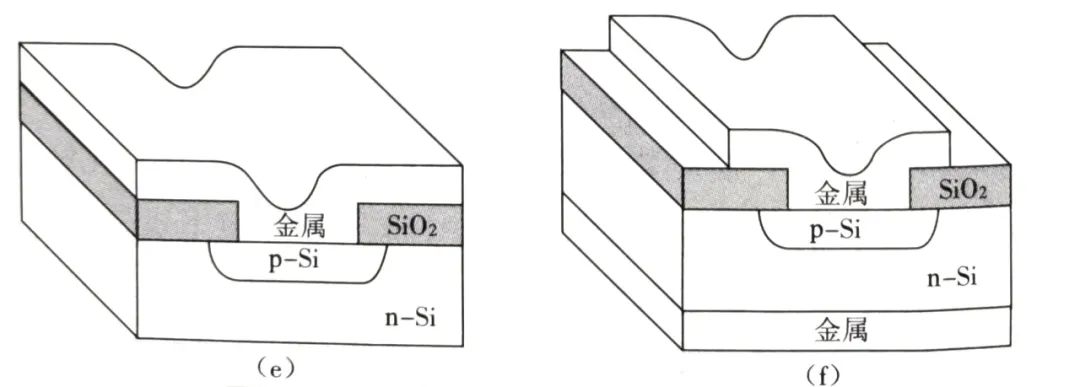

扩散或离子注入步骤以后,欧姆接触和互连线在随后的金属化工艺步骤中完成,如图3(e)所示。金属薄膜可以通过物理或化学气相淀积的方法形成。光刻的工艺再次被使用,以形成正面的金属连接,如图3(f)所示。在晶圆背面也要进行相似的金属化工艺处理,只是不进行光刻处理。一般来说,低温(≤500℃)退火工艺处理可用于增进金属层和半导体之间的低电阻接触。

图3 (e)金属化工艺处理后的晶圆;(f)完整工艺处理后的晶圆

审核编辑:黄飞