时间:2023-09-20 10:47

人气:

作者:admin

虽然真实芯片中,寄存器初始状态值只会为1或者为0。但是在RTL级仿真过程中X态的传播经常会给咱们造成很多麻烦,例如部分信号期望为0,但是仿真结果显示为X态。

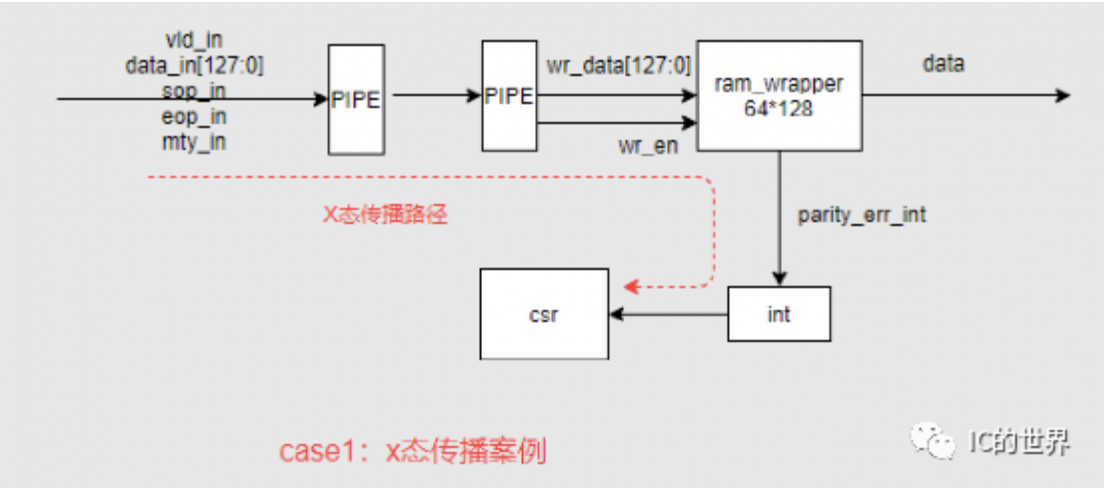

如下案例中:

入口数据mty_in[3:0]表示data_in[127:0]中无效的字节数,例如当数据最后一拍mty_in[3:0]为4’d2 表示data_in[127:0]中[15:0]是无效数据,由于入口数据是其他模块送给咱们的,有可能data_in[15:0]是X态,此时data_in[127:0]一路打拍写入了ram_wrapper,ram_wrapper存在parity_err_int计算逻辑,此逻辑的输入是wr_data[127:0],即源头是data_in的128bit,只要data_in[127:0]存在1bit X态,则计算得到的parity_err_int就是x态,最终会经过中断模块(int)传播到寄存器配置模块(csr)。NOTE: 真实的芯片中,不存在此bug。

这只是其中一个微不足道的小案例,类似的场景还有很多,X态传播给RTL仿真带了了很多麻烦。那有什么解决方案呢?这里有个小技巧:对输入数据进行X态隔离,让模块内部的信号都是稳定的状态。

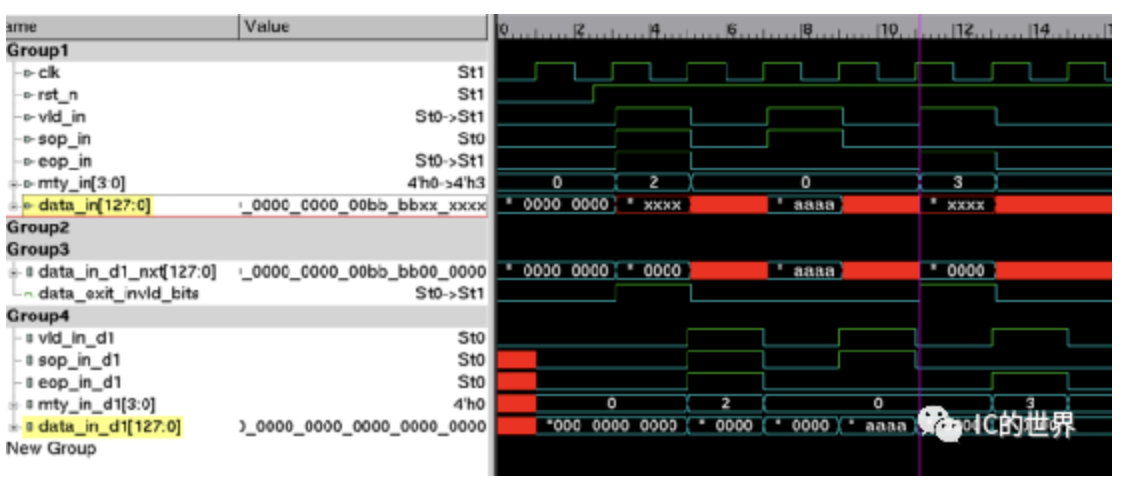

隔离效果如下:输入数据data_in在mty_in不为0时,存在值为x态的无效字节,而经过简单的处理后,模块内部的data_in_d1中所以bit均为稳定值,其无效字节被赋值成了0。

核心处理逻辑:data_exit_invld_bits为1时表示数据的最后一拍,且data_in存在无效字节,此时将data_in_d1_nxt赋值给data_in_d1。

module 以及简陋的testbench 代码:

`timescale 1ns/1ps

module x_state_handle_top ( ) ;