时间:2023-09-01 15:27

人气:

作者:admin

在芯片内部,信号一般都是通过并行传输的,因为串行传输实在是太慢了。然而芯片的IO都是串行传输的,并行传输对于硬件布局实在要求太高了,硬件工程师表示很头大。而且芯片IO是芯片的重要资源,怎么能让一组信号占用那么多呢!

芯片之间的串行数据传输对频率很敏感,因为高频会带来更大的噪声干扰、码间干扰、电磁干扰等,进而导致信号失真。

一般在芯片的低速串行IO,采用不同的沿来发送和接收来避免信号干扰对采样信号的影响,但是clk频率都在100M以内,比如SPI协议,I2C协议。

但是当信号频率到达几百M或者G以上,通过不同的沿来发送和接收信号,已经不能避免信号干扰的问题了,高频时钟受噪声干扰更为严重,到达采样端已经完全失真了。而且clk与data之间的skew约束更为严格,几乎不可能实现。

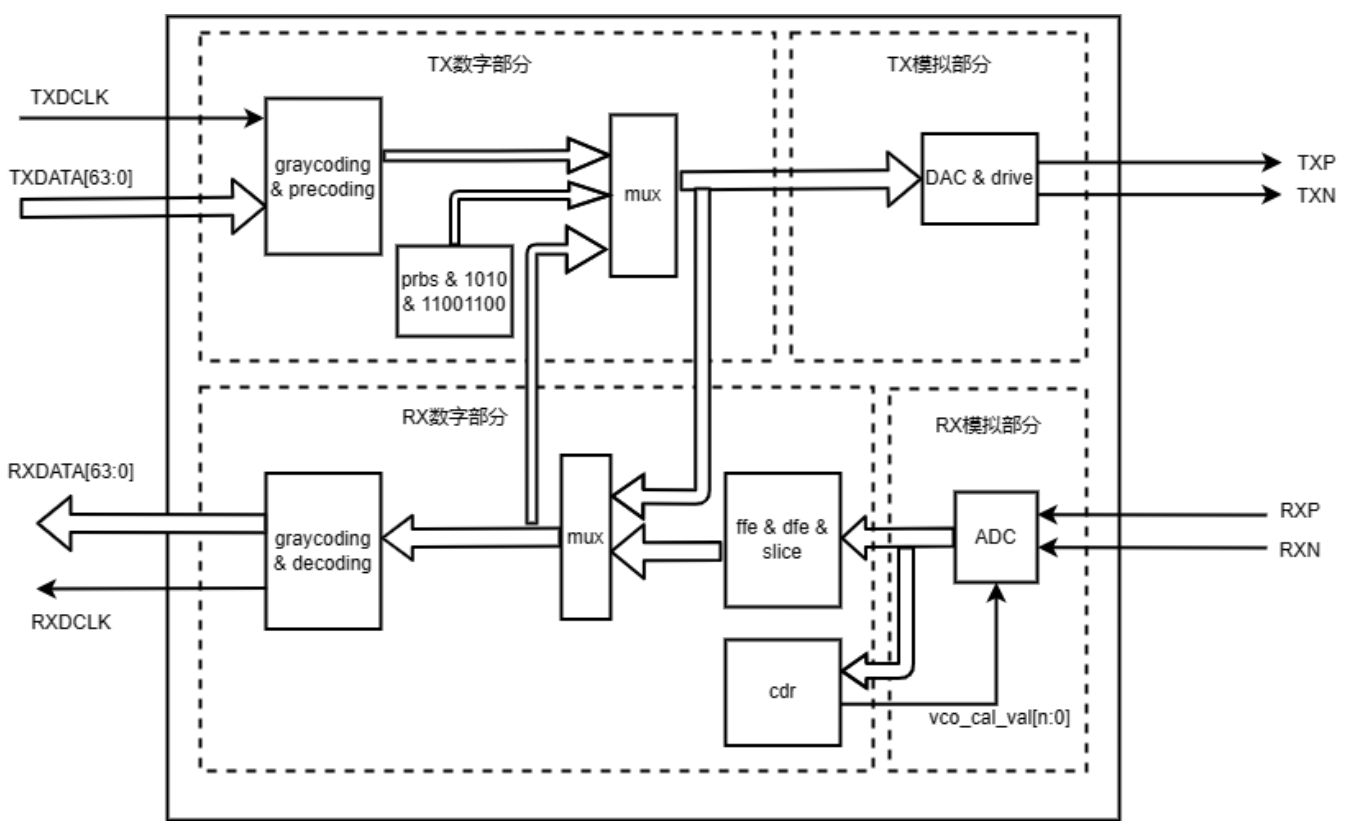

图1:Serdes 结构图

这个时候就需要应用serdes了,serdes包含了模拟和数字均衡来切实消除噪声干扰、码间干扰等。如下图所示,serdes的RX模拟部分在ADC采样之前有CTLE(线性均衡)来进行高频滤波,然后通过ADC采样模拟电平到数字域,然后通过CDR恢复数字时钟,通过FFE/DFE进行数字信号均衡,然后进行数据判决,最终将判决后的data输出给上层。

TX方向将输入的信号进行FFE均衡,然后输出给TX模拟部分发出给对端。通过发送端和接收端的一致均衡,来消除信道上未知的干扰。而且serdes可以从接收data里面恢复出采样时钟,避免了clk与data之间skew导致采样时序以及时钟失真的问题。

下一篇:2nm芯片设计成本曝光