时间:2023-02-20 14:16

人气:

作者:admin

可以看出,智能体并不像人类专家一样追求直线布局。为了优化布局,智能体更倾向于弧形布局。我们也希望能训练智能体高效地创造一些前所未有的布局方式。

为了实现这个目标,首先,我们运用强化学习算法优化某个芯片设计块的布局,期间需要经历上万次迭代;然后,重复前一步骤,在多个不同的设计块上预训练出一套布局规则,最终让算法在面对前所未见的新设计块时也能给出布局方案。

预训练好的策略有助于在推理时做更少的迭代,进行“零次(zero-shot)布局”。我们实际上还没有新算法来优化这个特定的设计,当然我们可以做数百次迭代以得到更好的结果。

上图展示了使用不同方法时的布局成本。蓝线表示不经过预训练的从头训练策略的布局成本,绿线表示用已预训练的算法优化新设计块的布局,X轴表示训练时间,可以看到,蓝线在经过20多小时的训练后方可大幅降低布局成本,此后仍需经过一段时间才能达到收敛。而绿线只用了极少的训练时间就达到了更低的布局成本并很快收敛。

最令我感到兴奋的是圈红部分。调优预训练策略在短时间内就可实现相当不错的布局,这种实现就是我所说的,在一两秒内完成芯片设计的布局。

上图展示了更详细的不同设计的情况。Y轴表示线长成本(越低越好)。绿色表示使用商业工具的线长成本,可以看到,从浅蓝色(零次布局)→蓝色(2小时微调)→深蓝色(12小时微调),线长成本越来越低。深蓝色一直比黄色的线长成本要低,因为通过12小时的微调能从其他设计中学到最佳布局。

上图展示了更详细的不同设计的情况。Y轴表示线长成本(越低越好)。绿色表示使用商业工具的线长成本,可以看到,从浅蓝色(零次布局)→蓝色(2小时微调)→深蓝色(12小时微调),线长成本越来越低。深蓝色一直比黄色的线长成本要低,因为通过12小时的微调能从其他设计中学到最佳布局。

上图中,左边和右边分别展示了从头训练的策略和经过微调预训练策略的芯片布局过程。每个小方块表示一个宏的中心,空白部分表示为标准单元预留的位置。可以看到,右边从一开始就将宏放在边缘,将大片中间区域留空。而左边则要经过很多次迭代才能形成这样的格局。

我们利用强化学习工具针对TPU v5芯片的37个设计块进行了布局与布线。其中,26个设计块的布局与布线质量优于人类专家,7个设计块的质量与人类专家相近,4个设计块的质量不如人类专家。目前我们已经把这个强化学习工具投入到芯片设计流程中了。

总的来说,用机器学习进行芯片布局与布线的好处包括:可以快速生成多种布局方案;即使上游设计有重大改动也可以迅速重新布局;大幅减少开发新ASIC芯片所需的时间和精力。

接下来是芯片设计的验证阶段。我们希望用较少的测试次数覆盖多个测试项目。验证是阻碍芯片设计提速的主要瓶颈。据估计,芯片设计过程中,80%的工作量在于验证,而设计本身仅占20%。因此,验证技术的任何一点进步都会产生重大作用。

Google在2021年NeurIPS(神经信息处理系统大会)上发表了论文《Learning Semantic Representations to Verify Hardware Designs》,我们能不能运用机器学习生成在更短时间内覆盖更广状态空间的测试用例?

验证阶段的基本问题是可达性(reachability)。目前的芯片设计能否让系统达成需要的状态?我们的想法是,根据当前的芯片设计生成一个连续的表示,从而预测对系统的不同状态的可达性。

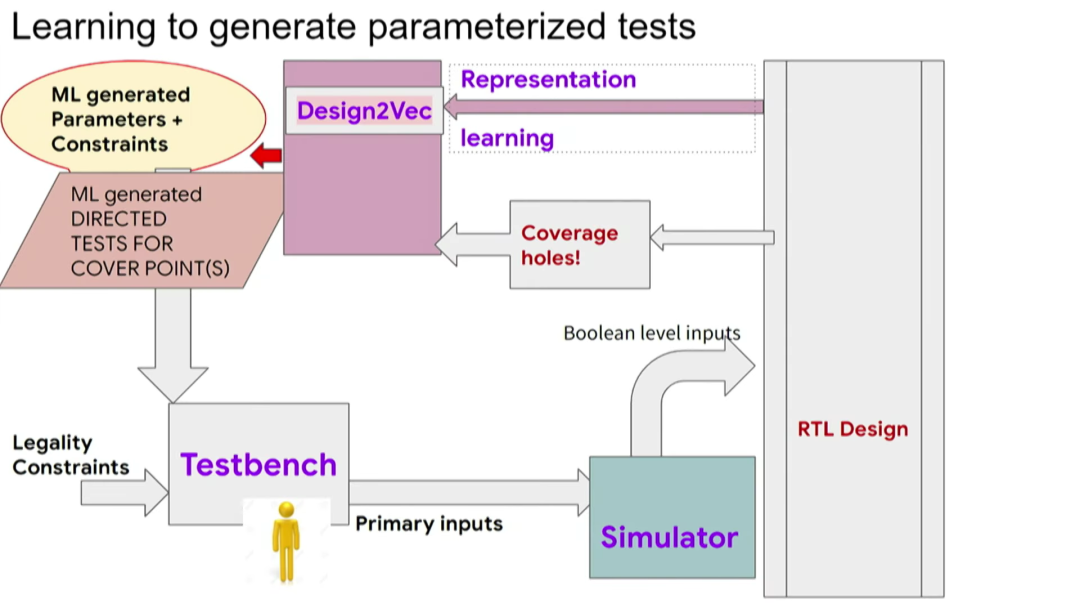

我们可以通过RTL将芯片设计抽象为一张图,然后运用基于图的神经网络去了解该图的特性,从而了解其对应芯片设计的特性,继而决定测试覆盖率和测试用例,这给了我们一个很好的设计的抽象表示。

当然,如何将这种方法应用到实际芯片设计中将是另外一个重要话题。用RTL生成图表示之后,我们在图神经网络中运用一种叫Design2Vec的技术进行深度表示学习,从而帮助我们作出预测。

目前,芯片的验证环节需要大量人力,例如,找bug、查找测试覆盖率漏洞、分析和解决bug等,还需要经历多次如上图所示的流程循环。我们希望上述步骤可以实现自动化,自动生成新的测试用例以解决重要的问题。

后来我们发现,可以把这个问题转化为一个监督学习问题。如果之前进行了一系列测试,并知道这些测试覆盖哪些测试点,就可以将这些数据用作监督学习中的训练数据。

然后,当出现新的测试点时,假设进行一个新的测试,我们需要预测这个测试能否覆盖新的测试点。我们希望能结合之前的训练数据以及芯片设计本身,来实现这种预测。

我们有两个Baseline,其中一个能够看到测试点(test points)和覆盖点(cover points)的数据,这是一个黑盒测试。

而Design2Vec除了能够处理上述数据外,还能处理实际设计、设计的图结构等等。如果你使用一半的测试点作为训练数据,并且设置多个大小不同的训练集,然后对其它测试点进行预测,那么将会得到非常出色的结果,即使是对于相对较少的覆盖点,也能泛化得非常好。相比之下,Baseline这种方法就不能对此进行很好地泛化。

但使用图神经网络来学习设计、覆盖率和测试属性的方法,实际上比NeurIPS论文中的其他所有Baseline都要好。

例如,我们常会遇到很多难以生成测试的覆盖点。工程师们发现使用RISC-V Design和TPU Design这两种不同的设计也很难为这些特定的覆盖点生成测试,于是我们又转向使用贝叶斯优化器来尝试生成测试。

上图右边这一列是贝叶斯优化器覆盖的不同测试点、覆盖点所需的模拟器调用数(simulator calls),中间一列是使用Design2Vec所需的模拟器调用数。从中可以看到,为覆盖这些有挑战性的覆盖点,Design2Vec生成的测试要少于贝叶斯优化器。所以Design2Vec非常好,相比之下它更快,能聚焦覆盖范围,还能节省在运行计算模拟器(本身很昂贵)上的开销。

验证是芯片设计在理论和实践上长期面临的一个挑战。我们认为,深度表示学习能够显著提高验证效率和质量,并且在设计中实现泛化。

即使设计发生了一些改变,这个新设计的版本也能运用之前在众多设计上训练出来的系统,提高验证效率。正如在布局与布线阶段,经过训练后的算法即使面对新设计也能够预测不同测试的覆盖点,以带来好的结果。

上一篇:机器学习如何影响计算机硬件设计1

下一篇:机器学习如何影响计算机硬件设计3