小编在本节完整给出一个设计过程,可利用ISE或Vivado硬件编程软件实现。

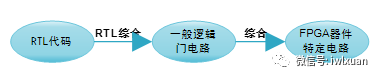

1 HDL代码、逻辑电路和器件

- 编写“HDL代码”来描述电路功能

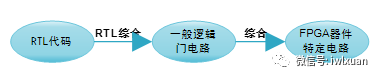

- EDA工具中进行“RTL综合”和“综合”

“RTL综合”将HDL代码转换为逻辑电路

“综合”这一步将经过“RTL综合”后的门电路映射为FPGA器件的物理结构 - “实现”这一步将对FPGA器件进行最终的布局布线

- 综合实现的结果将会被转换为可以最终运行在FPGA器件上的二级制烧录文件

2 HDL代码实例

- 在每个时钟clk信号的上升沿,实现输出信号dout的值为输入信号ain、bin和cin的2级门运算的结果

- 这个门运算先是ain和bin“逻辑与”,它们得到的结果再和cin“逻辑或”

- 输入复位信号rst_n为异步复位信号,任何时刻这个信号的下降沿将直接触发输出信号dot取值为0

举个栗子

module at7(

clk,rst_n,

ain,bin,cin,dout

);

input clk;

input rst_n;

input ain,bin,cin;

output reg dout;

always @(posedgeclk or negedgerst_n)

if(!rst_n)

dout <= 1'b0;

else

dout <= (ain & bin) | cin;

endmodule

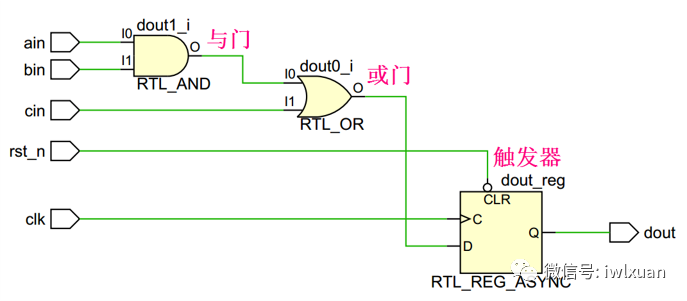

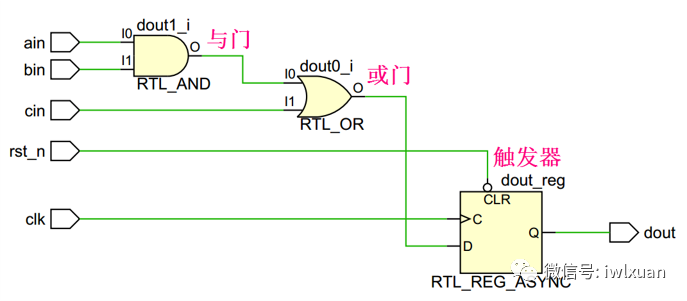

3 RTL综合

- “RTL综合”后的逻辑电路原理图,它很好的以门电路的形式表达了我们的实例代码

- “RTL综合”门电路和HDL代码所描述的功能完全一致,大家对比下图和第2节的代码。下图即是代码RTL综合后的布局。

图1 RTL综合后的逻辑电路原理图

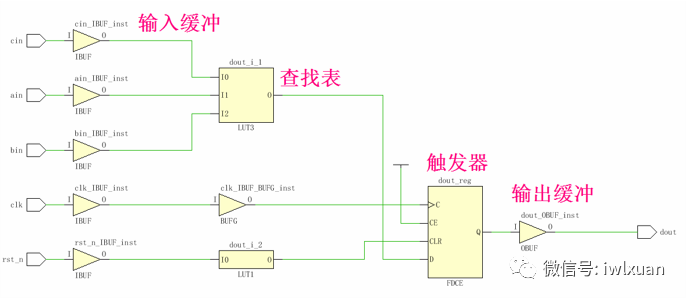

4 综合

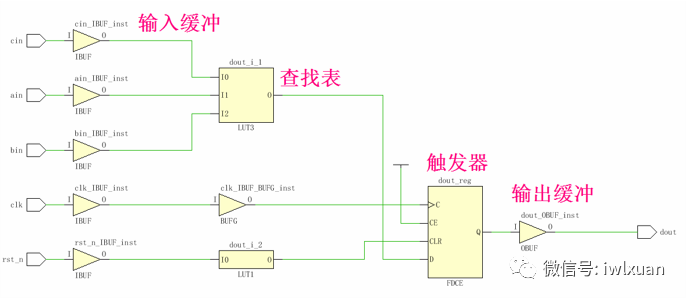

- “RTL综合”是指将HDL代码转换为逻辑门电路形式来表达的一个过程;“综合”却是将已经用逻辑门关系表达的电路进一步转换为FPGA器件实际物理结构相对应的电路形式 “综合”电路中看不到任何的“门”

- “综合”的结果是所使用的特定FPGA器件中实际存在着的物理结构,如“输入缓冲”、“查找表”、“触发器”和“输出缓冲”等

图2 RTL综合与综合的关系

图3 综合后的逻辑电路原理图

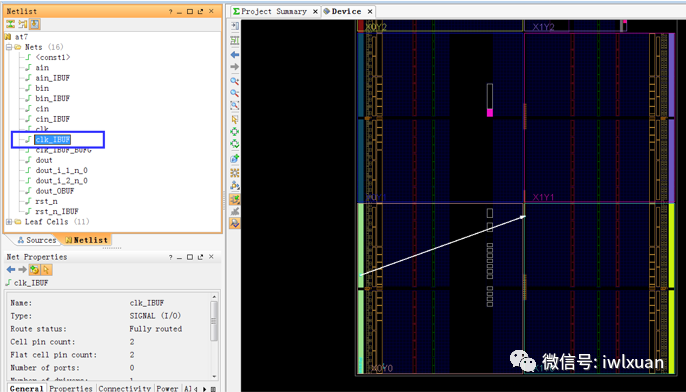

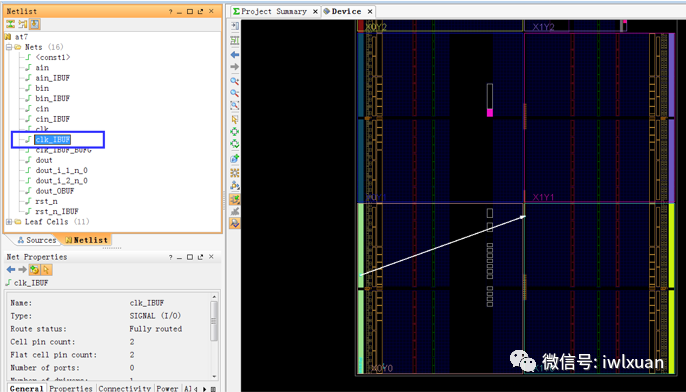

5 实现

- 在“综合”给出HDL代码与实际FPGA器件的映射关系后,做具体执行的工作

- 如果把“综合”结果比喻为电路板设计的“原理图”阶段,那么“实现”这个步骤就是具体的“布局布线(layot)”阶段

图4 布线图

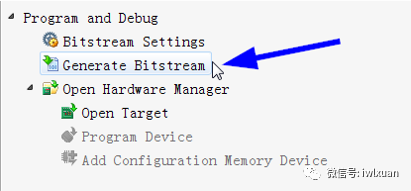

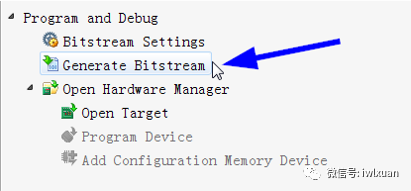

6 生成烧录文件

- 如同电路板的layout完成后要生成gerber,FPGA工具最终也要产生一个bit文件用于烧录到FPGA中运行了