时间:2023-07-17 15:00

人气:

作者:admin

什么是同步有限状态机?

同步:所有的状态跳转都是在时钟的作用下进行

有限:状态的个数是有限的

为什么要用状态机?

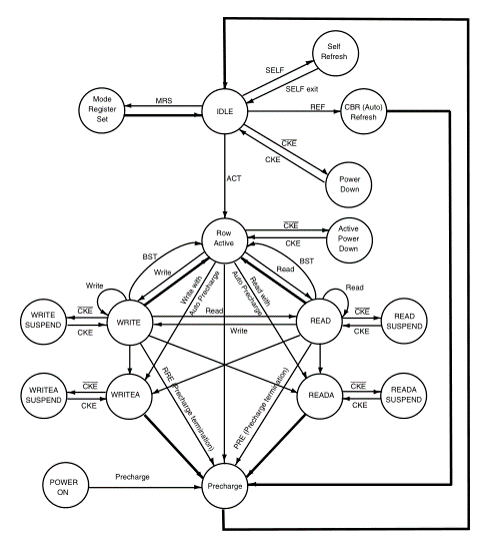

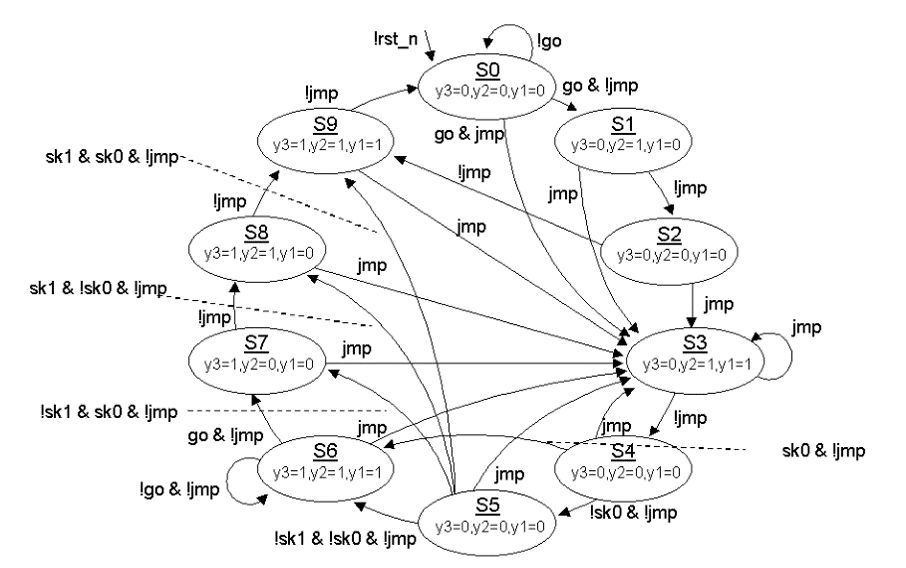

FPGA是并行处理的,如果我们想要处理具有前后顺序的事件时,就需要引入状态机。状态机的每一个状态代表一个事件,从执行当前事件到执行另一事件我们称之为状态的跳转或状态的转移。

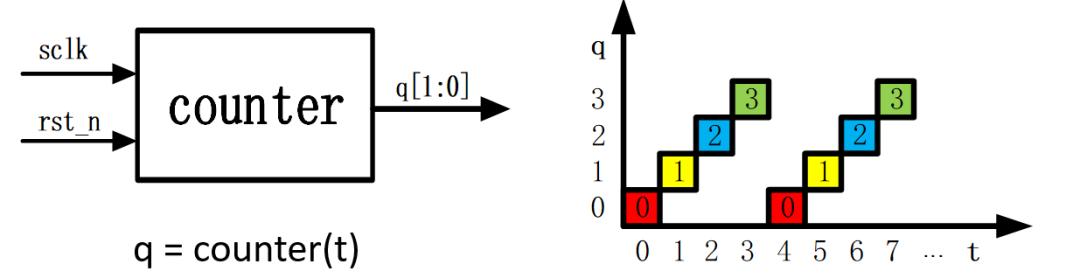

状态机特别适合描述那些发生有先后顺序或时序规律的事情。小到计数器大到微处理器都适合用状态机描述。

怎么表示状态机?

状态机需要具备什么?

状态机的设计步骤是怎么样的?

FIFO的使用

什么是FIFO?

FIFO(First In First Out)即先入先出,是一种数据缓冲器,用来实现数据先入先出的读/写方式。FIFO有一个写端口和一个读端口外部无需使用者控制地址,使用方便。

根据FIFO工作的时钟域可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。异步FIFO是指读/写时钟不一致,是相互独立的。

FIFO的作用是什么?

如何使用FIFO?

FPGA设计中的技巧

一、使能信号(en)、标志信号(flag)、计数器(cnt)

二、模块框图设计——方案的确定

三、波形设计——代码的实现

四、代码规范——可复用性和效率

五、仿真调试——修改查错

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有