时间:2022-06-16 10:16

人气:

作者:admin

引言

Preface

随着芯片设计规模的增加,传统基于单颗 FPGA 的设计调试方法已经不能满足对大型设计的调试需求,因此多 FPGA 联合调试技术应运而生。

本次国微思尔芯白皮书《先进多FPGA联合深度调试方法剖析》分析了用户在进行大规模原型验证过程中的多 FPGA 联合调试难题,并介绍了一种新型 FPGA 原型验证深度跟踪调试解决方案,用于帮助客户在 SoC 开发过程中解决调试问题,从而加速设计验证、缩短验证周期。本调试解决方案还提供了不同使用模式,可以用于灵活适配不同用户的使用场景。

核心内容

Main Point

大规模原型验证调试中的挑战

传统的基于单颗 FPGA 的设计调试方法是在单颗 FPGA 中插入嵌入式逻辑分析仪的方式进行调试的,这种调试方式适用于 单颗 FPGA 的独立调试应用场景。但是随着设计规模的增长,当单颗 FPGA 无法满足原始设计规模时,原始设计就会被分割到多颗 FPGA 中,在此应用场景下传统基于单颗 FPGA 的设计调试方法存在各种问题。

多FPGA的深度跟踪调试解决方案

针对 SoC 原型验证系统中调试需求,本文提出了一种多 FPGA 的深度跟踪调试解决方案。主要包含以下内容:

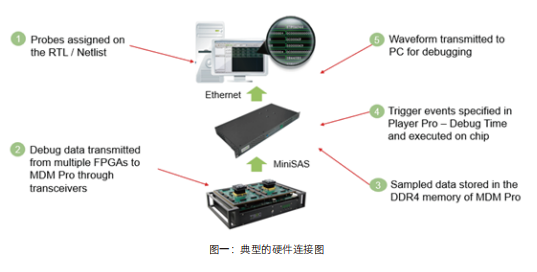

硬件连接及工作流程

基于调试 IP 的探针信号标记过程

基于 GT 的调试信号传输

基于 DDR4 的波形数据存储

基于以太网的波形数据上传和远程调试

基于外部高速采样时钟和内部逻辑时钟采样

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有