时间:2023-06-06 17:07

人气:

作者:admin

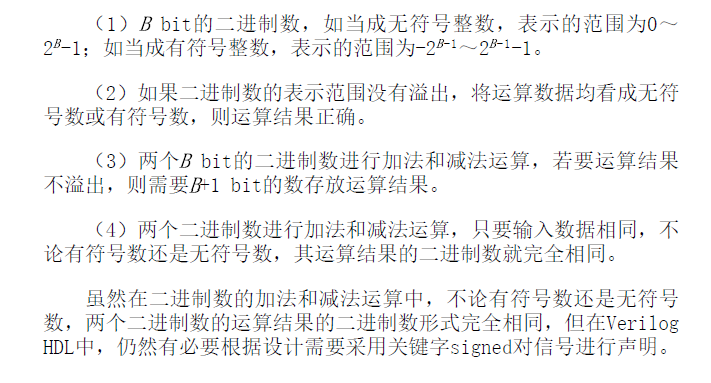

加、减 使用补码时,加减法可以统一,因而对加减不加区分,对有无符号也不加以区分。

为了不丢失进位,M位+N位时,设M>=N,则结果需要M+1位储存结果

图源:Xilinx FPGA数字信号处理设计:基础版 (杜勇),下同

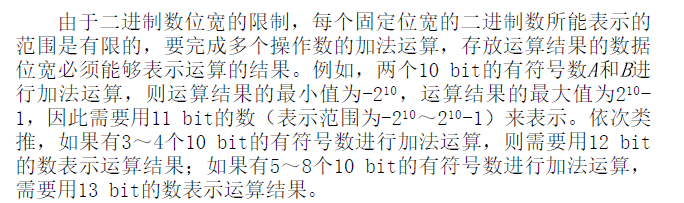

当多个数据累加时,显然多一位存储结果,结果能够表示2倍(无符号数);当拥有3-4个操作数时,结果的最大值为4倍的单个操作数表示的最大值,因而增加2bit即可;类似的5-8个操作数,最大为8倍,因而增加3bit即可

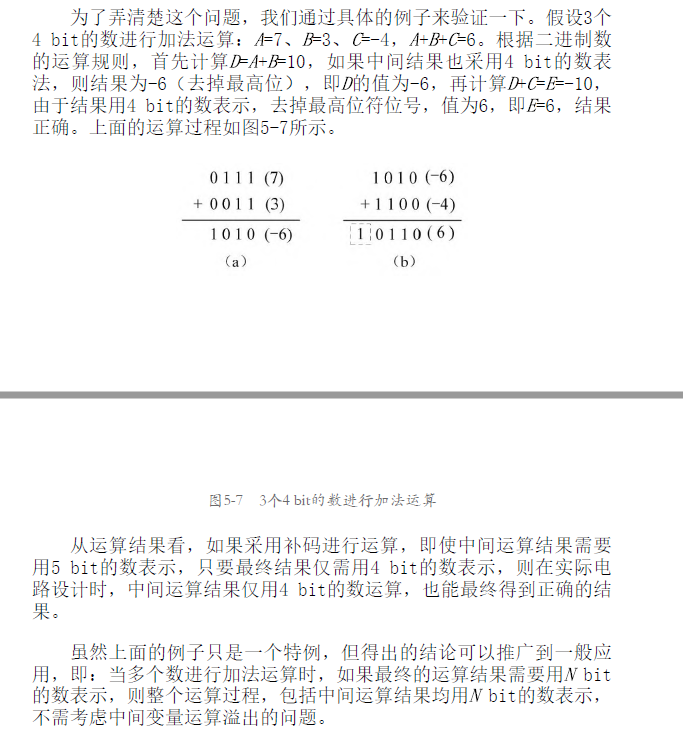

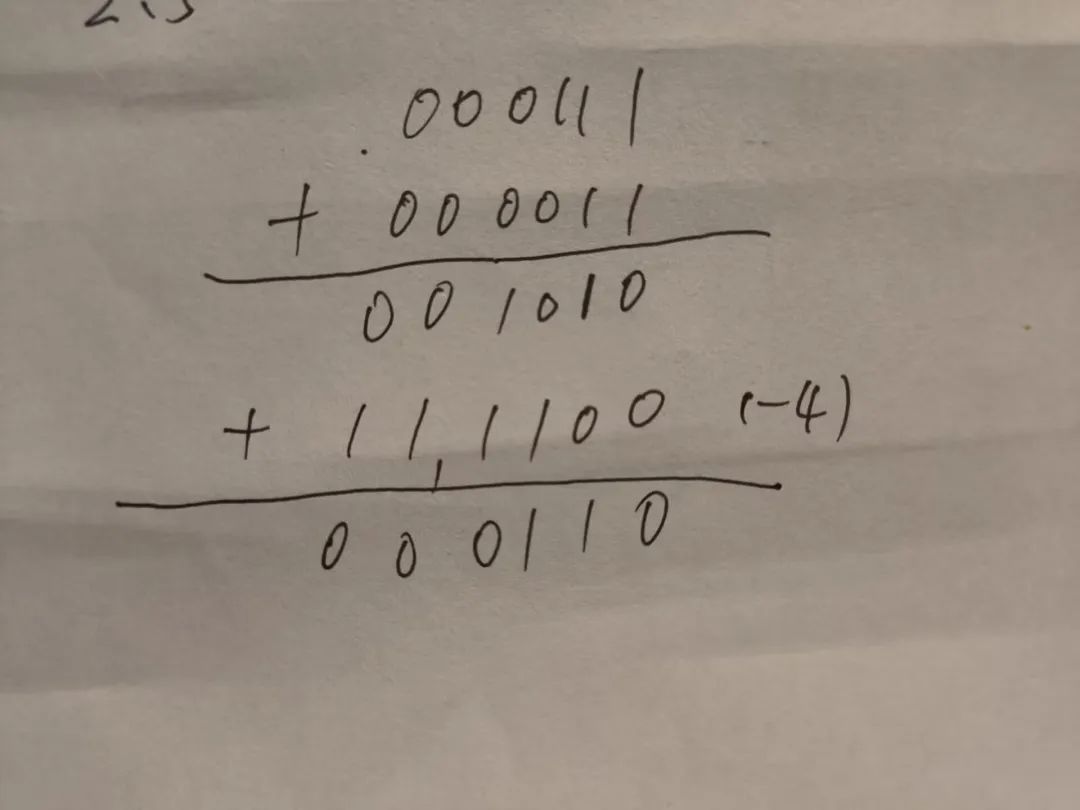

另一方面,当计算结果能够被约束时,不加证明地,存在一个结论:多个数相加,若结果需要Nbit即可,计算的中间值也只需Nbit

上面的计算过程若按照6bit运算过程如下,结果是一致的

2、乘法

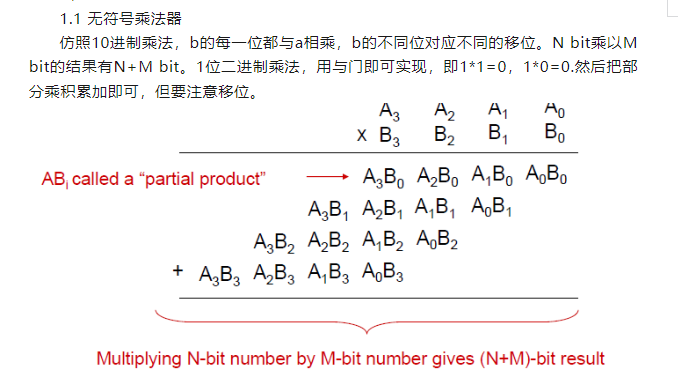

对于无符号数,N位*M位将得到N+M位的结果。可以直观的证明,如下图移位相加,N*M将移位(M-1)次,从而至少有(N+M-1)位,若加法出现进位,还需要额外1bit,共(N+M)位

有符号数,最高位需要表征符号,同样进行无符号乘法,再确定符号。因而N*M的有符号数,可以看成(N-1)*(M-1)的无符号数相乘,结果需要N+M-2位,还需要增加符号位,因而总共需要N+M-1位。

3、除法

除法更为简单,M/N,对于整数而言,N的绝对值大于等于1,因而商最大和M一样,只需要M位就行。

4、more

当结果位宽不够,会进行截断,带来丢失精度的计算结果。

审核编辑:刘清

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有