时间:2023-04-20 09:38

人气:

作者:admin

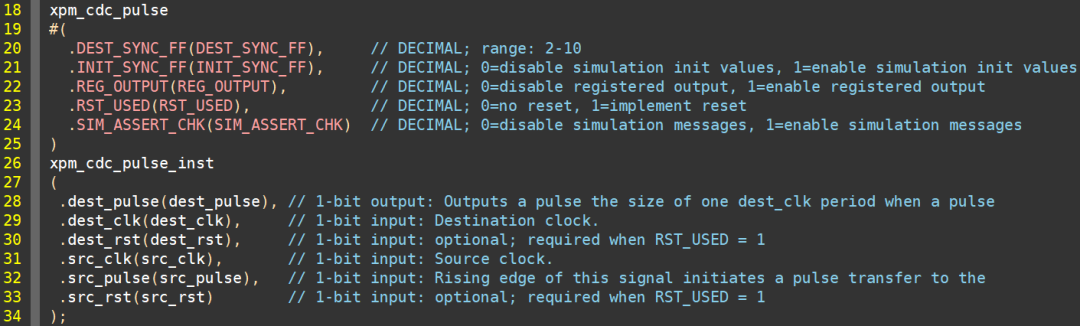

对于脉冲信号跨时钟域,XPM_CDC提供了模块xpm_cdc_pulse,如下图所示。该模块有5个参数,其中参数DEST_SYNC_FF用于确定级联触发器的个数;INIT_SYNC_FF用于确定仿真时是否使用触发器初始值;

参数REG_OUTPUT用于确定是否对最终输出信号寄存;参数RST_USED用于确定是否使用复位信号;参数SIM_ASSERT_CHK则用于确定是否显示仿真信息。从输入/输出端口来看,源端时钟域的输入信号为src_pulse和src_rst;

目的端时钟域的输入信号为dest_rst,输出信号为dest_pulse(src_pulse跨时钟域后的结果)。

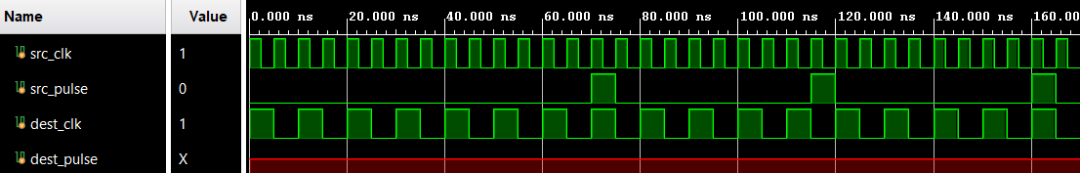

这些参数对仿真以及实际电路都有较大影响。如果参数INIT_SYNC_FF为0,同时RST_USED也为0,这就表明了仿真时不能使用同步寄存器链路的初始值,同时也没有复位信号对其复位,这样仿真时就会出现未知态,如下图所示。

审核编辑 :李倩

上一篇:“简约而不简单”的射频开关设计

下一篇:10道题看你对电路了解多少

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有