时间:2023-05-11 16:16

人气:

作者:admin

我一直没搞明白BUFIO是干嘛用的。

官方解释有这么一段话,如下:(virtex的)

“BUFIO是用来驱动I/O列内的专用时钟网络,这个专用的时钟网络独立于全局时钟资源,适合采集源同步数据。BUFIO只能由位于同一时钟区域的Clock-Capable I/O驱动。一个时钟区域有4个BURIO,其中的2个可以驱动相邻区域的I/O时钟网络。BUFIO不能驱动逻辑资源(CLB、BRAM等),因为I/O时钟网络只存在于I/O列中。”

就是如果BUFIO只能驱动IO,到达不了CLB和RAM,可是数据最终是要进逻辑的啊,为什么呢?

首先、需要明确BUFIO是输入用的。BUFIO是用来驱动输入时钟的,将外部时钟引入FPGA的!与IOBUF不同啊,但与IBUFG类似,时钟信号进FPGA也可以经过IBUFG。

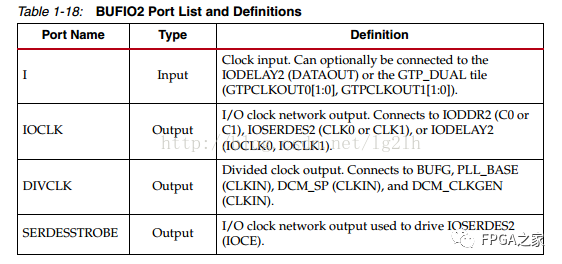

其次、再来看BUFIO的输入和输出:SPARTAN6 的UG382手册里这么写的,如下:

BUFIO2 can drive ISERDES2 and OSERDES2 for either SDR or DDR clocking. BUFIO2 can

also route clock inputs from either a GCLK or a GTP_DUAL tile to a BUFG, DCM, or PLL

clock input. BUFIO2_2CLK can be used to replace one of the BUFIO2s required for DDR

clocking of the ISERDES2 and OSERDES2

(SDR:单边沿,DDR:双边沿)

就是说BUFIO2输入可以是GCLK(全局时钟)和GTP_DUAL。然后输出到BUFG或者,DCM ,PLL的时钟输入。

也就是说数据流顺序 PAD-->BUFIO-->BUFG或者PAD-->BUFIO-->DCM(PLL)--->BUFG不知道有这样用的吗。

但实际应用可以这样,BUFIO配和ISERDES2使用,ISERDES2是将串行数据转成并行数据,相当于分频了。而BUFIO具有分频的功能。

举例串行数据转成4bit并行数据:串行数据相当4分频,同样将随路时钟clk_in(就是和串行数据同步进来的时钟,,作为串行数据的采集时钟)同步BUFIO接进FPGA,

BUFIO可以将输入的随路时钟clk_in进行4分频为clk_in4。这样把clk_in4给BUFG,然后就可以同步将4bit的数据输入采集到逻辑FIFO中去了。

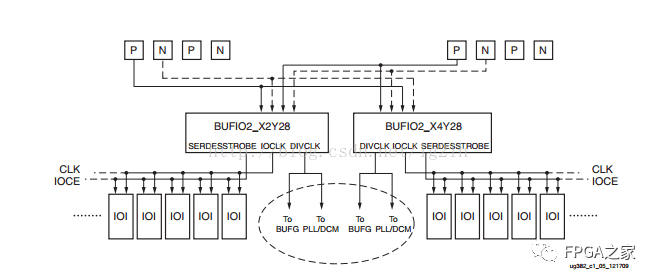

配个图,看看BUFIO的输入输出可以接什么:

输出链接示意图,如下:可以看到PN-->BUFIO-->BUFG(DCM)或者PN-->BUFIO-->IO,驱动IO(PN只差分对的P和N)

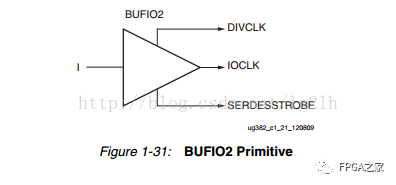

结合一下BUFIO的原语结构:

可以看出:

以上是对SP6讲的,在virtex里面,有文章开头那句话:BUFIO是用来驱动I/O列内的专用时钟网络,这个专用的时钟网络独立于全局时钟资源,适合采集源同步数据。BUFIO只能由位于同一时钟区域的Clock-Capable I/O驱动。一个时钟区域有4个BURIO,其中的2个可以驱动相邻区域的I/O时钟网络。BUFIO不能驱动逻辑资源(CLB、BRAM等),因为I/O时钟网络只存在于I/O列中。”

就是说virtex里面BUFIO好像只能由Clock-Capable I/O驱动了。

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有