时间:2023-03-31 09:07

人气:

作者:admin

1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64;win7/32;win10/64

软件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

2.2.1主要功能

1)产生基带原始数据

2)完成2FSK调制

3)完成2FSK解调

2.2.2主要性能指标

1) 调制端

系统时钟:50MHz

基带数据码率:390.625kbps

载波频率:3MHz

调制度:3.5

2) 解调端

系统时钟:50MHz

采样频率:25MHz

解调方式:非相干

位同步:超前-滞后型数字锁相环位同步

3 程序结构框图说明

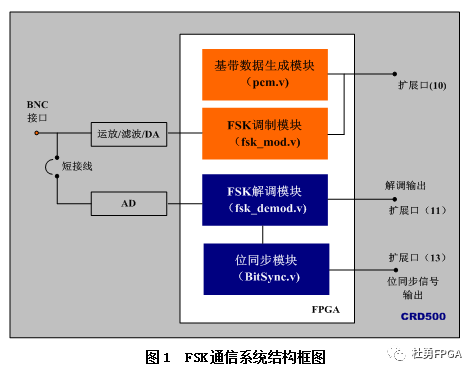

FSK通信系统主要由基带数据生成模块(pcm.v)、FSK调制模块(fsk_mod.v) 、FSK解调模块(fsk_demod.v)和锁相环位同步模块(BitSync.v)组成。

基带数据生成模块生成的原始数据(390.625kbps)送至FSK调制模块完成连续相位FSK调制,同时将原始数据流送至CRD500开发板上扩展口的第10脚,便于用示波器测试。FSK调制模块对接收到的原始数据进行FSK调制。调制度为3.5,载波频率为3MHz,则码元0对应的频率为3M-3.5/2*390.625k=2.31640625MHz, 码元1对应的频率为3M+3.5/2*390.625k=3.68359375MHz。

调制后的数据经CRD500的DA/滤波/运放电路转换成模似信号经跳线送出;采用短接帽将调制后的模拟信号送至CRD500的AD采样电路,转换成数字信号后送至FPGA处理;FSK解调模块完成FSK信号解调,并将解调出的数据送至扩展口的第11脚。

解调判决后的数据送至位同步模块提取位同步信号,将提取出的位同步信号送至扩展口的第13脚输出。为真实验证FSK通信功能,发送端(pcm.v和fsk_mod.v)的时钟由CRD500开发板上的X1晶振驱动,接收端(fsk_demod.v)的时钟由X2晶振驱动。

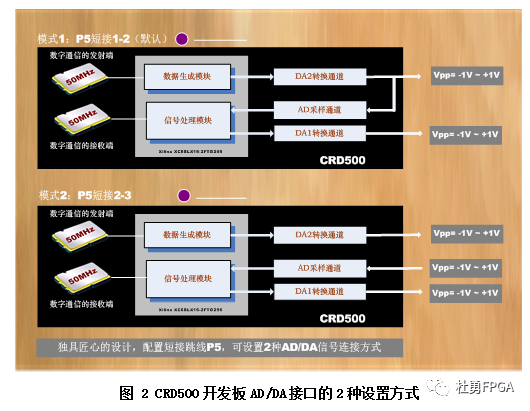

CRD500板上AD/DA接口有多种设置方式,如图2所示。

本次工程实例采用图2中的模式1连接方式。如果采用图2中的第2种模式,则需要采用双头BNC线将AD接口与DA接口连接起来。

审核编辑:刘清

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有