时间:2023-02-08 11:48

人气:

作者:admin

1 运行平台

硬件:CXD301数字信号处理板

系统:win7/64;win7/32;win10/64

软件:ISE/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

3.2.1主要功能

1)产生基带原始数据

2)帧同步信号提取

3.2.2主要性能指标

1) 发送端

系统时钟:50MHz

基带数据码率:195.3125kbps

数据内容:帧长16位,帧同步字长7位,同步字为1011000

2) 接收端

系统时钟:发送端送来的数据时或信号,195.3125kbps

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数可通过修改程序参数快速设置。

3 程序结构框图说明

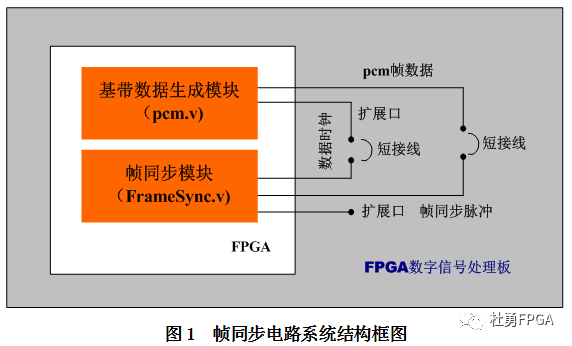

帧同步电路系统主要由基带数据生成模块(pcm.v)、帧同步模块(FrameSync.v)模块组成。

基带数据生成模块生成的原始数据(1.5625Mbps)送至开发板上扩展口,经短接线由第35脚送回FPGA芯片;数据生成的同步时钟信号也经扩展口硬件环回至帧同步模块。为便于测试环路同步及失步状态,输入端设计了一个数据选择控制逻辑,通过按键控制输入数据。

审核编辑:刘清

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有