时间:2023-02-16 10:47

人气:

作者:admin

1)尽可能采用单一时钟;

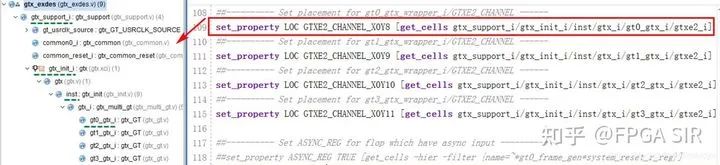

2)如果有多个时钟域,一定要仔细划分,千万小心,同时设置时序约束;

1)尽可能采用单一时钟;

2)如果有多个时钟域,一定要仔细划分,千万小心,同时设置时序约束;

3)跨时钟域的信号一定要做同步处理;

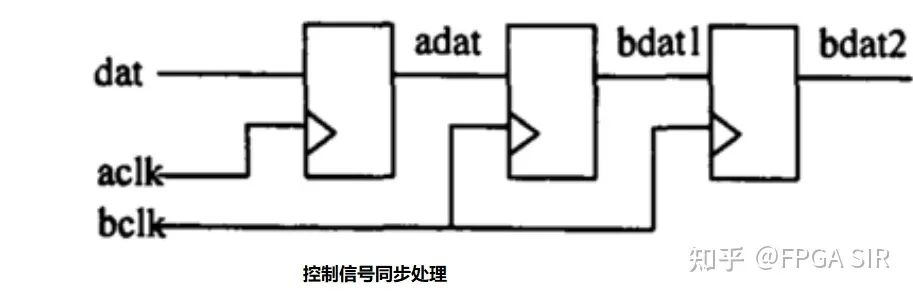

对于控制信号的异步处理是寄存器打两拍缓存;

3)跨时钟域的信号一定要做同步处理;

对于控制信号的异步处理是寄存器打两拍缓存;

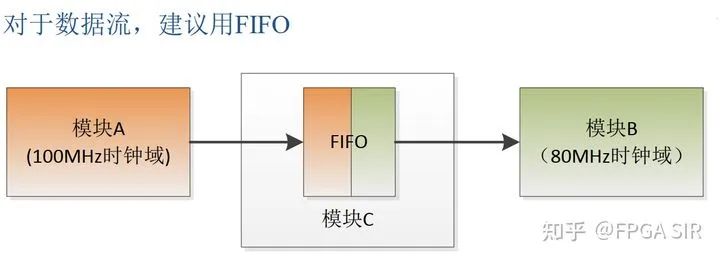

对于数据信号的异步处理是异步fifo缓存,同时注意FIFO两侧的数据流的速率问题;

对于数据信号的异步处理是异步fifo缓存,同时注意FIFO两侧的数据流的速率问题;

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处;

5)对于高速的IO接口,需对高速IO设置的delay约束。

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处;

5)对于高速的IO接口,需对高速IO设置的delay约束。

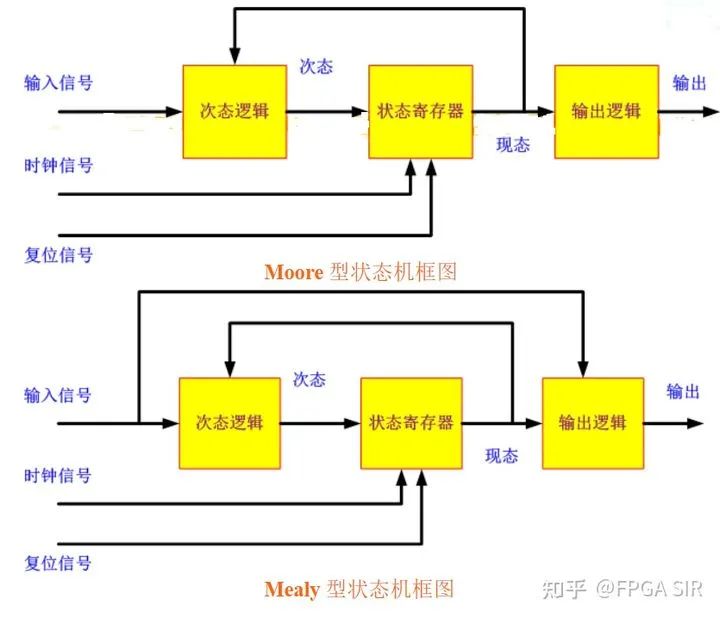

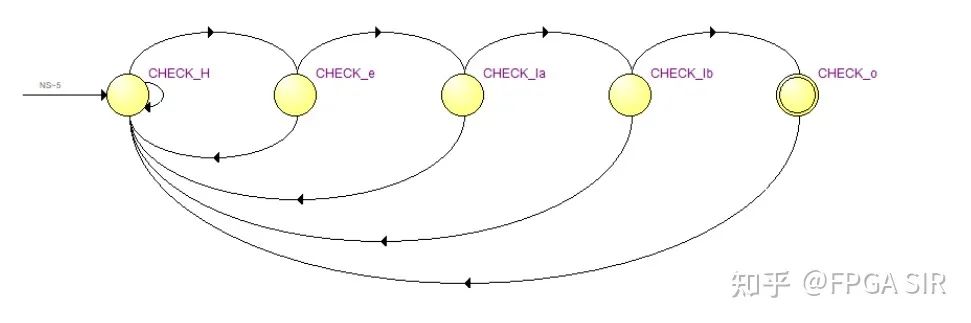

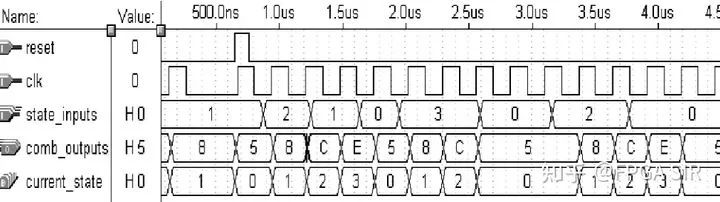

FSM:有限状态机,FPGA最基本的程序设计之一。FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。

FSM:有限状态机,FPGA最基本的程序设计之一。FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。

实际使用中大部分都采用merly型。

状态机的编码:二进制编码(Binary),格雷码编码(Gray-code),独热码(One-hot)。

实际使用中大部分都采用merly型。

状态机的编码:二进制编码(Binary),格雷码编码(Gray-code),独热码(One-hot)。

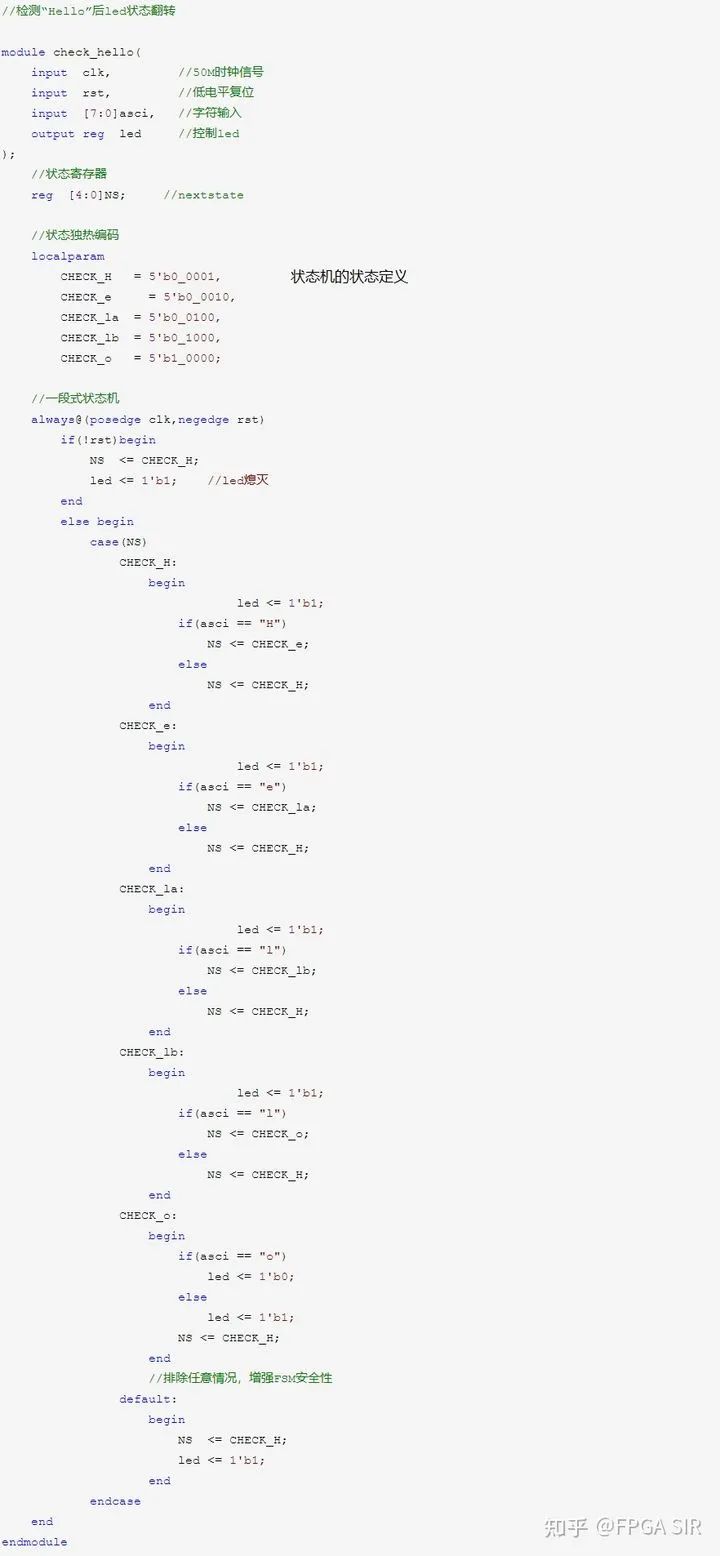

状态机FSM一段式FPGA编码参考。

状态机FSM一段式FPGA编码参考。

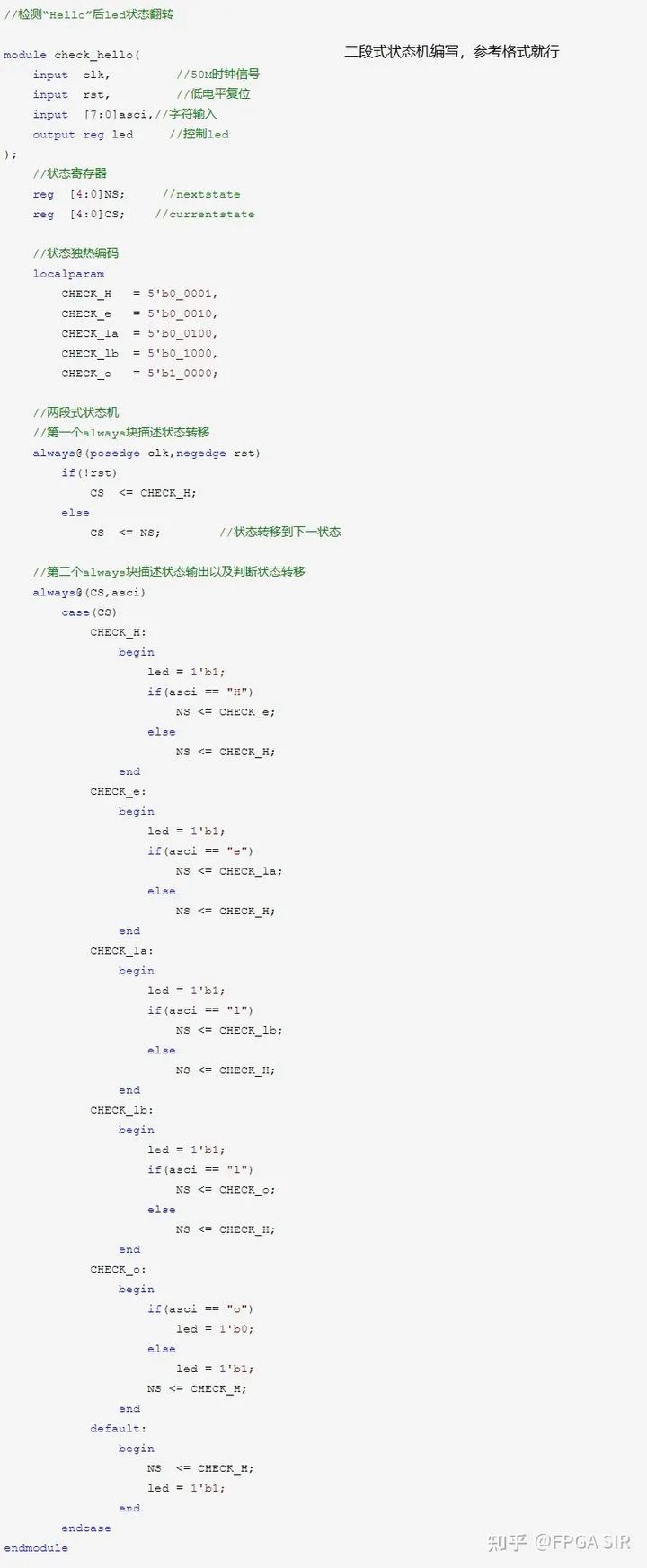

状态机FSM二段式FPGA编码参考。

状态机FSM二段式FPGA编码参考。

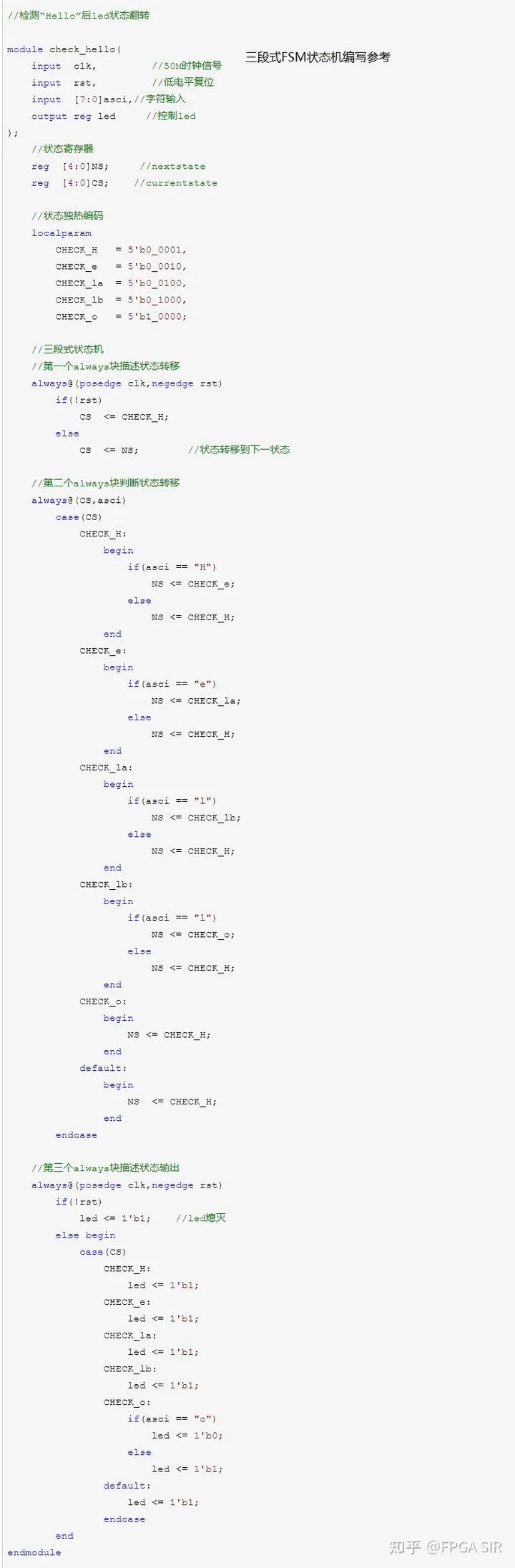

状态机FSM三段式FPGA编码参考。

状态机FSM三段式FPGA编码参考。

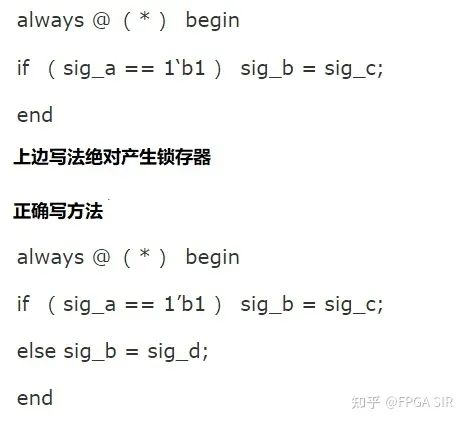

1)在组合逻辑always块中,if语句一定要有else。

2)在组合逻辑always块中,case语句的default一定不能少。

3)组合逻辑进程敏感变量不能少也不能多。

1)在组合逻辑always块中,if语句一定要有else。

2)在组合逻辑always块中,case语句的default一定不能少。

3)组合逻辑进程敏感变量不能少也不能多。

1)模块仿真:针对每一个最小基本模块的仿真;

单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%,这三种覆盖率都可以通过modelsim来查看,不过需要在编译该模块时要在Compile option中设置好。

1)模块仿真:针对每一个最小基本模块的仿真;

单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%,这三种覆盖率都可以通过modelsim来查看,不过需要在编译该模块时要在Compile option中设置好。

2)集成仿真:将多个大模块合在一起进行仿真,覆盖率要求尽量高;

3)系统仿真:将整个硬件系统合在一起进行仿真。

此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。

审核编辑 :李倩

2)集成仿真:将多个大模块合在一起进行仿真,覆盖率要求尽量高;

3)系统仿真:将整个硬件系统合在一起进行仿真。

此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。

审核编辑 :李倩

下一篇:基于FPGA的图像处理

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有