时间:2020-11-26 14:16

人气:

作者:admin

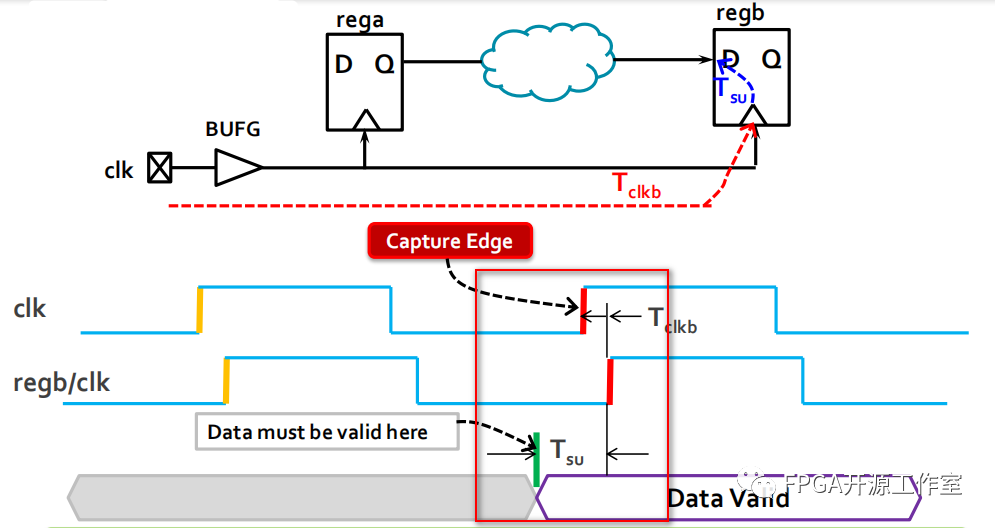

典型的时序模型由发起寄存器、组合逻辑和捕获寄存器3部分组成,如图1所示形成了三条时钟路径:原时钟路径(Source Clock path)、数据时钟路径(Data path)、目的时钟路径(Destination Clock path)。

1、建立时间(setup)和保持时间(hold)

如图1所示,时钟上升边沿(Capture Edge 、Next Launch Edge)会将数据保存下来,但是必须要满足一定的条件:

A,建立时间Tsu:在时钟有效沿之前,数据必须保持稳定的最小时间;

B,保持时间Th:在时钟有效沿之后,数据必须保持稳定的最小时间;

这就相当于一个窗口时间,在有效边沿的窗口时间内,数据必须保持稳定;这里的时钟信号时序和数据信号时序,都是寄存器实际感受到的时序。

2、发起沿和捕获沿

如图1所示,发起沿和捕获沿通常相差一个时钟周期同时捕获沿也是下一个发起沿。

发起沿(LaunchEdge):数据被launch的时钟边沿;也就是说,每一个启动沿,一般都会产生一个新的数据!

捕获沿(CaptureEdge):数据被latch的时钟边沿;也就是说,每一个锁存沿,都会有一个新的数据被保存!

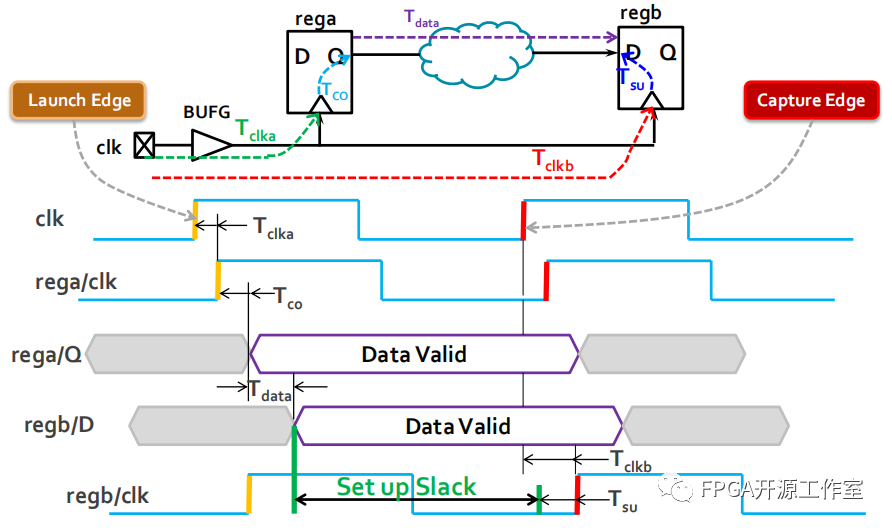

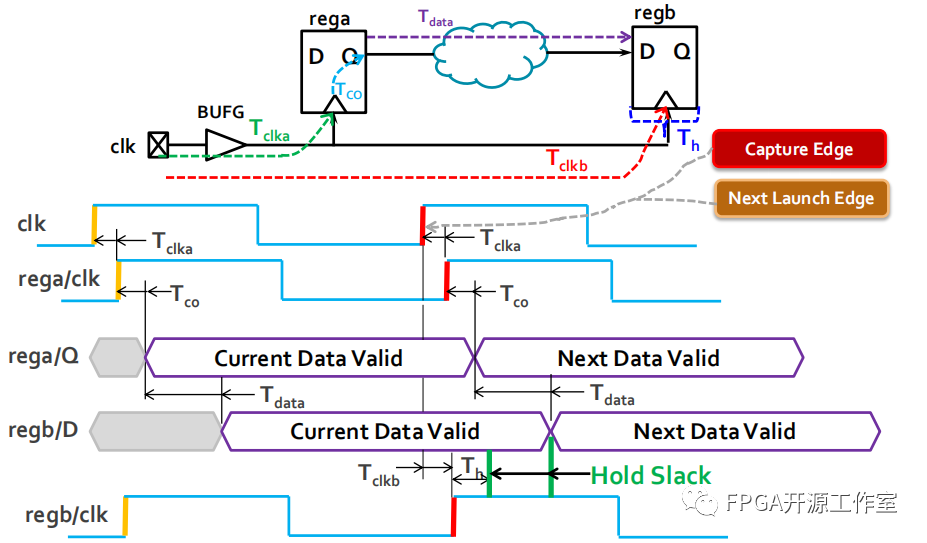

3、时序模型2

如图2所示:

Clk--时钟源

Rega--发起寄存器

Regb--捕获寄存器

Tclka--原时钟延时

Tclkb--目的时钟延时

Tco--发起沿有效到数据出现在发起寄存器Q端口所需时间

Tdata--数据延时(组合逻辑和走线延时)

Tsu--捕获寄存器建立时间

Th--捕获寄存器保持时间

4、数据到达时间(Data Arrival Time)

数据到达时间(Data Arrival Time)=Launch Edge +Tclka+Tco+Tdata

已发起沿为时间参考点,LaunchEdge 通常为0。

5、数据建立需求时间(setup)

数据建立需求时间(DataRequired Time(setup)) = Tclkb-Tsu-Clock Uncertainty

表明数据必须提前Tsu稳定存在于捕获寄存器的输入端口。

6、数据保持需求时间(hold)

数据保持需求时间(DataRequired Time(hold))=Tclkb +Th-Clock Uncertainty

表明数据必须在时钟捕获沿(regb/clk)之后稳定存在一段时间Th。

7、建立时间裕量(Setup Slack)

建立时间裕量(SetupSlack)= Data Required Time(setup)-Data Arrival Time(setup)

如果SetupSlack为正,则说明数据在规定的时间内达到了目标。反之,则认为数据并没有在规定的时间达到目标,此时REG2锁存的数据很有可能存在亚稳态。

8、保持时间裕量(Hold Slack)

保持时间裕量(holdSlack)=DataRequired Time(hold)-Data Arrival Time(hold)

如果为正,则认为数据在被锁存的时候有足够多的稳定时间,是有效的。反之则认为数据有误或者数据可能存在亚稳态。

编辑:hfy

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有