时间:2020-09-28 10:57

人气:

作者:admin

Versal™ ACAP(自适应计算加速平台)是高度集成化的多核计算平台,可通过灵活的自适应能力来满足不断变化的动态算法的需求。VCK190 是赛灵思最早发布的 Versal AI Core 评估器件之一。

本篇博文将为您详解如下所述设计创建步骤:

1. 在 Vivado 中构建基于 Versal 的 IP 集成器 (IP integrator) 设计

2. 创建器件镜像

3. 在 Vitis 中构建平台和系统工程

4. 在 VCK190 评估板上运行和调试应用

Versal上的PS-GEM

千兆以太网 MAC (GEM) 可提供符合 IEEE 802.3-2016 标准的硬核 10/100/1000 Mbps 接口。

在 PS 低功耗域 (LPD) 中有 2 个 GEM 控制器。

每个控制器均独立运行,且各含 1 个管理数据输入/输出 (MDIO) 接口以供其外部 PHY 配合 RGMII 接口使用。

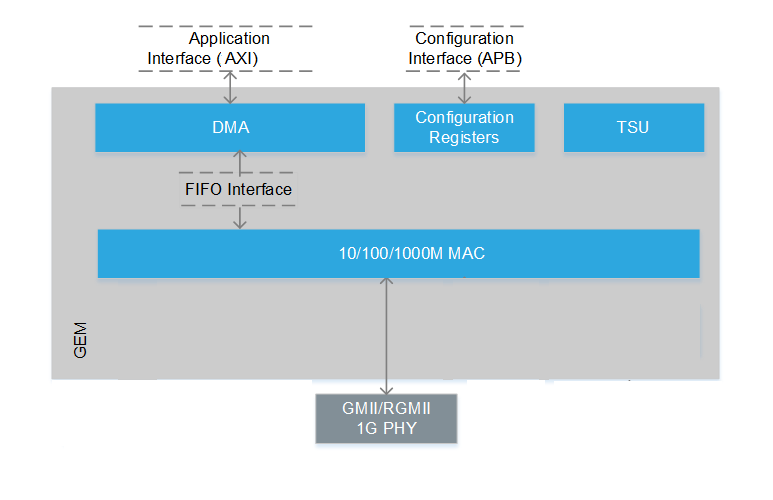

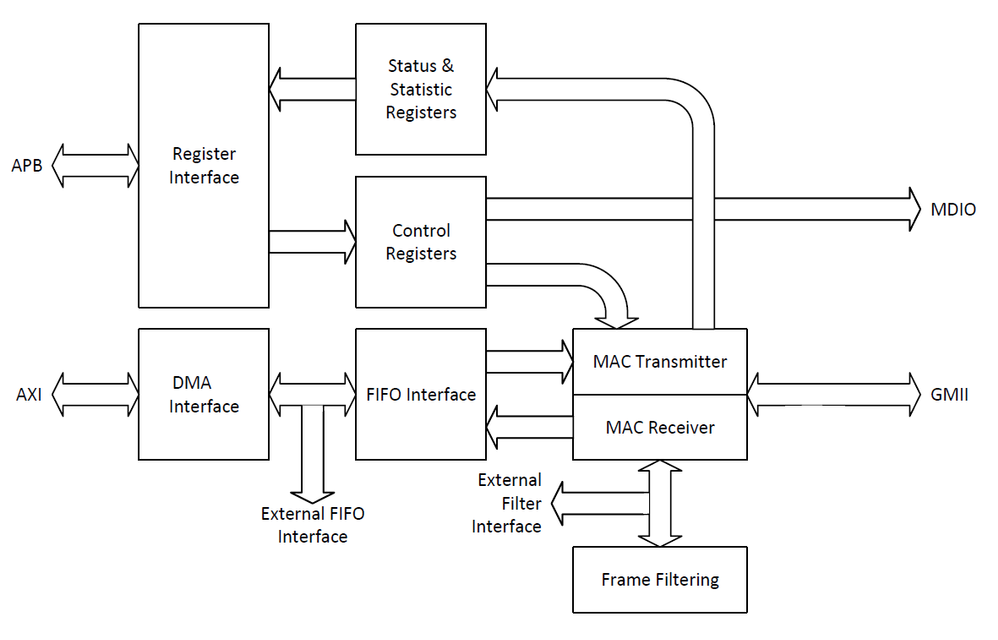

GEM 包含下列组件:

1 个 MAC 用于控制传输、接收、地址检查和环回

配置寄存器,可提供控制和状态寄存器、统计数据寄存器和同步逻辑

1 个直接内存访问 (Direct Memory Access) 模块,用于控制 DMA 传输和 DMA 接收

1 个时间戳单元 (TSU),用于计算 IEEE 1588 定时器值,其中包含实时时钟

在无需 DMA 操作的系统应用中,可使用配置选项移除 DMA 模块,并且可使用外部 FIFO 接口将 GEM 集成到 SoC 环境中。

GEM 块包含以下信号接口:

连接到外部 PHY 的 GMII 和 RGMII

1 个用于外部 PHY 管理的 MDIO 接口

1 个 APB 从接口,用于访问 GEM 寄存器

1 个用于内存访问的 AXI4 DMA 主接口

无需 DMA 功能的应用内包含 1 个可选 FIFO 接口

1 个可选时间戳接口

I/O 选项包括:

布线到 LPD MIO 管脚的 RGMII (v2.0),用于连接到外部 PHY

GMII 和 MII 布线到 PL,以便映射到 GT 或(可选)可借助 PL 逻辑来转换为其它协议

每个控制器内的诊断内部环回

注:Versal 中不支持内部 SERDES 接口 (SGMII)。在 MPSoC 器件中支持此类接口。

在 VCK190 器件上,GEM0 和 GEM1 均硬连线到板上的 2 个外部 RGMII PHY。

有 2 个 RJ45 端口,分别用于 GEM0 和 GEM1。如要测试 GEM1 RGMII 端口,请确保 GEM0 RGMII 端口同样通过电缆连接,因为此端口使用共享 MDIO 线(使用 GEM0 MDIO 作为主接口)。

请参阅以下 VCK190 截屏。在右上角有 2 个 RJ45 端口用于 Versal 以太网。

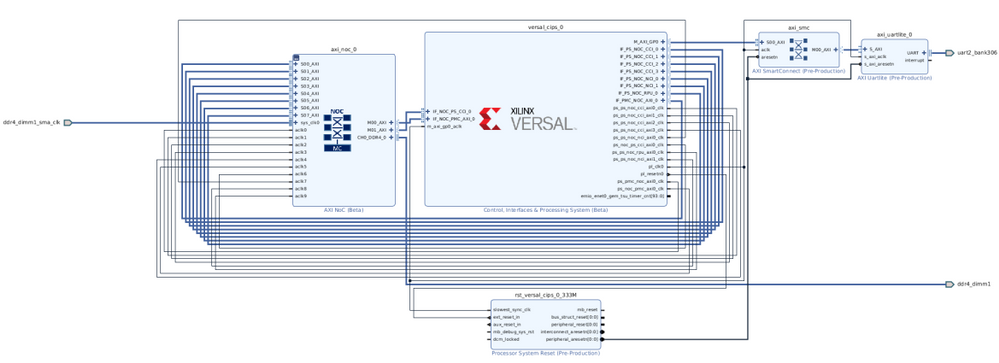

在 Vivado 中创建 IP integrator 设计

请下载随附的 Tcl 文件并遵循以下步骤进行操作。

1. 在 Vivado 2019.2 中基于 VCK190 评估板创建工程。

2. 创建块设计。

3. 找到 vck190_1g.tcl。以下是 IP integrator 画布中的原理图。

4. 生成 HDL 封装文件。

5. 单击“运行实现 (Run Implementation)”和“生成器件镜像 (Generate Device Image)”。

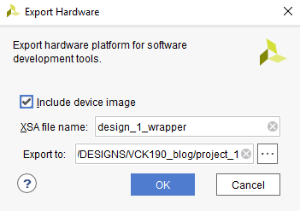

6. 导出包含器件镜像的硬件设计。

注:单独使用“运行块自动化设置功能 (run block automation)”时,CIP 与 NoC 之间部分连接缺失。随附的 Tcl 文件可用于确保 CIP 和 NoC 中配置设置正确。

在 Vitis 中构建并运行 LwIP 应用

我们已构建了 IP integrator 设计并已导出了含器件镜像的硬件设计。现在,我们将在 Vitis 中创建 lwIP 示例,并在 VCK190 评估板上运行。

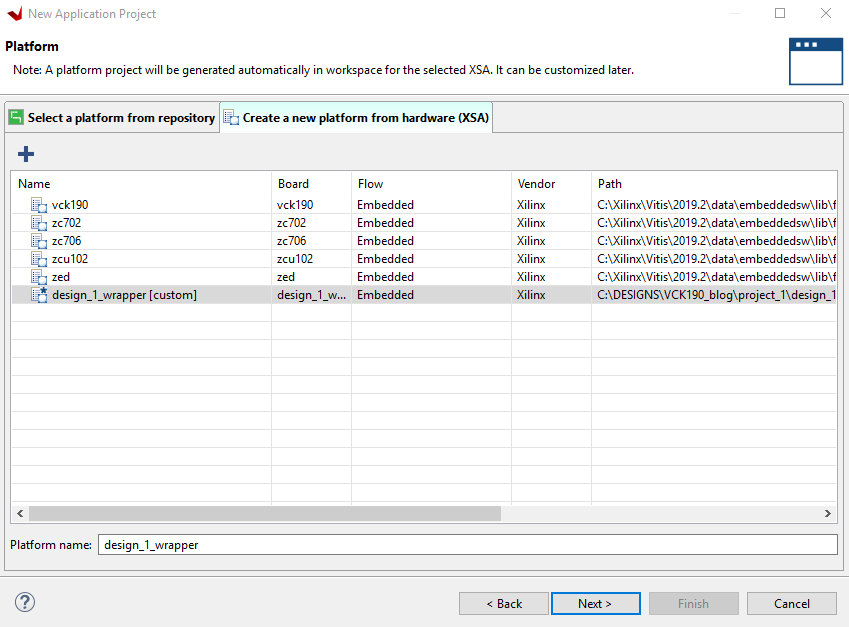

1. 启动 Vitis。

2. 使用来自以上设计的 XSA 文件创建应用工程。

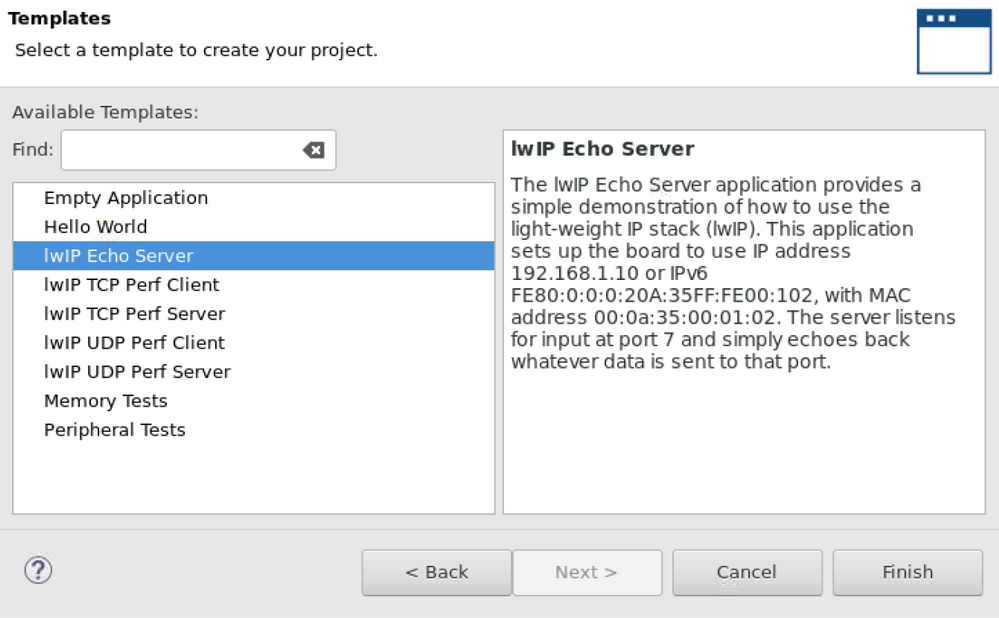

3. 从 SDK 中选择“lwIP 响应服务器 (lwIP Echo Server)”。

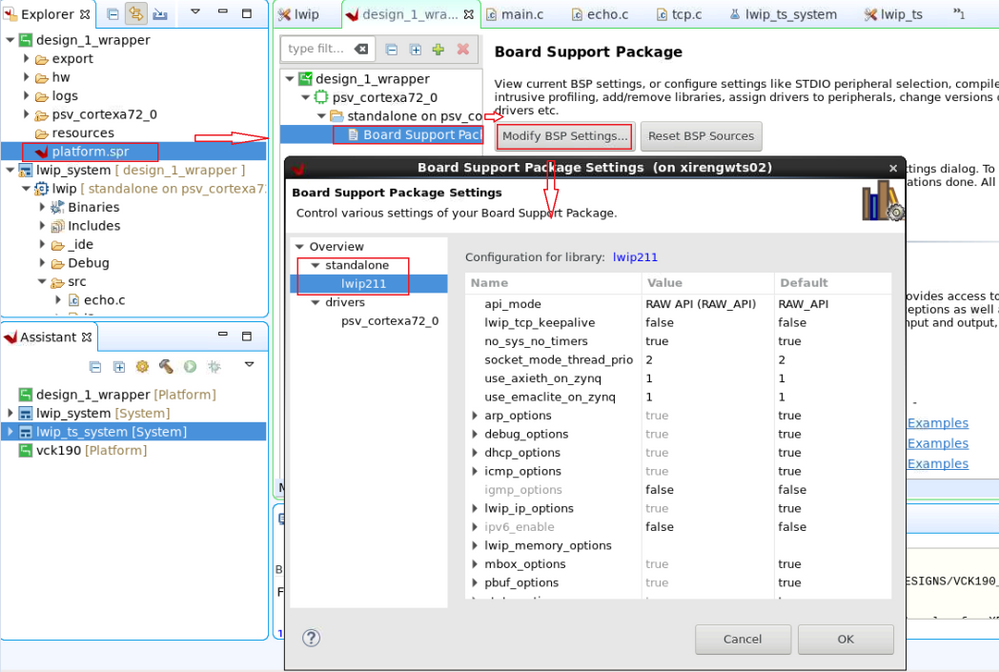

4. 在 SDK 中构建平台和系统工程。选中 lwIP 响应服务器应用时,会自动设置 lwIP 库的 BSP 设置。用户还可以选择仅创建并构建平台工程,但这样需手动设置 BSP 设置。

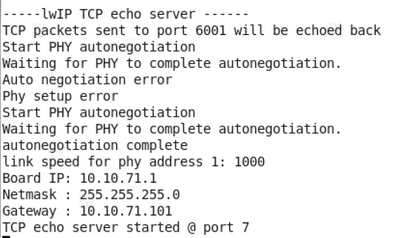

5. 在 VCK190 开发板上运行 lwIP 示例。以下即 UART 控制台输出:

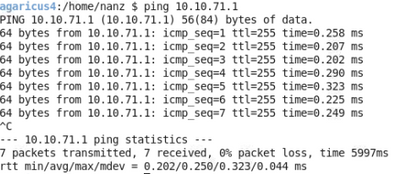

6. 以下是 ping 测试输出:

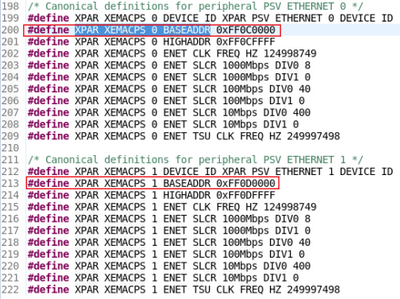

要切换到 GEM1 RJ45 以便进行测试,用户应使用 XPAR_XEMACPS_1_BASEADDR 修改 platform_config.h。

可在 BSP 的 xparameters.h 中找到以太网定义。请参阅以下示例

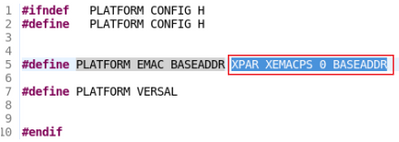

在 platform_config.h 中,更改以下定义:

将此定义更新为:

#define PLATFORM_EMAC_BASEADDRXPAR_XEMACPS_1_BASEADDR

现在,您可重新构建应用并重新运行测试。

LwIP性能

以下是 lwIP 响应服务器应用的 BSP 设置。

PARAMETER dhcp_does_arp_check = true

PARAMETER lwip_dhcp = true

PARAMETER pbuf_pool_size = 2048

对于 lwIP TCP/UDP 性能服务器,默认将设置下列参数。

PARAMETER mem_size = 524288

PARAMETER memp_n_pbuf = 1024

PARAMETER n_tx_descriptors = 512

PARAMETER pbuf_pool_size = 16384

这些 lwIP 参数对于性能调优至关重要。

这些参数可控制所分配和使用的内存量以及 Pbuf 和描述符数量。

如果系统受到限制,无法处理这些包,则 BD 和 Pbuf 将被快速用尽,且无法根据要求快速清空以供使用。由此导致性能受到影响。

但我们还应平衡可使用的内存量,以便在用于性能基准测试的评估板上将这些参数调整为适合 1Gbps 的最优值。您可以此为参考,根据自己的要求来对这些参数进行调优。

编辑:hfy

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有