时间:2023-09-28 11:43

人气:

作者:admin

Chiplet也称芯粒,通俗来说Chiplet模式是在摩尔定律趋缓下的半导体工艺发展方向之一,是将不同功能芯片裸片的拼搭,在某种意义上也是不同IP的拼搭,像拼接乐高积木一样用封装技术整合在一起,借此可以实现对先进制程迭代的弯道超车,在提升性能的同时实现低成本和高良率。

Chiplet与先进封装的关联

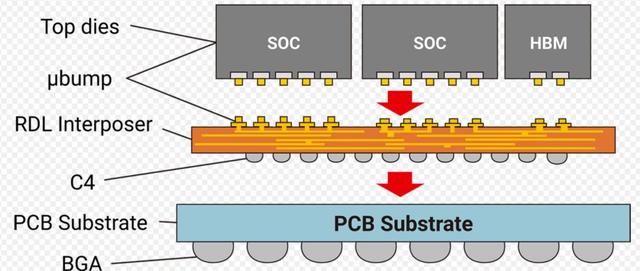

先进封装与Chiplet是两个概念,但采用Chiplet时大概率会采用先进封装。比如最经典的2.5D封装CoWoS(ChiponWaferonSubstrate)就是这样的,它是一颗Interposer(硅中介层)上放很多Die,这些Die你可以把它叫做小芯片,这个是Chiplet。

所以虽然Chiplet和3D先进封装不是同一个东西,需要通过先进封装技术,像搭积木一样把许多小芯片模块(Chiplet)集成在一起,去实现整个集成以后的芯片系统。

图片来源:台积电

先进封装是实现Chiplet的前提

芯片上数据的输入和输出 (I/O) 是计算芯片的命脉。处理器必须与外部世界进行数据的发送和接收。摩尔定律使业界的晶体管密度大约每2年增加2倍,但 I/O数据的传输速率每4年才增加2倍,所以芯片需要容纳更多的通信或I/O点才能跟上晶体管密度的增加速度。

Chiplet对先进封装提出更高要求。在芯片小型化的设计过程中,需要添加更多I/O来与其他芯片接口,裸片尺寸有必要保持较大且留有空白空间,导致部分芯片无法拆分,芯片尺寸小型化的上限被pad(晶片的管脚)限制。

并且单个晶片上的布线密度和信号传输质量远高于Chiplet之间,要实现Chiplet的信号传输,就要求发展出高密度、大带宽布线的“先进封装技术”。

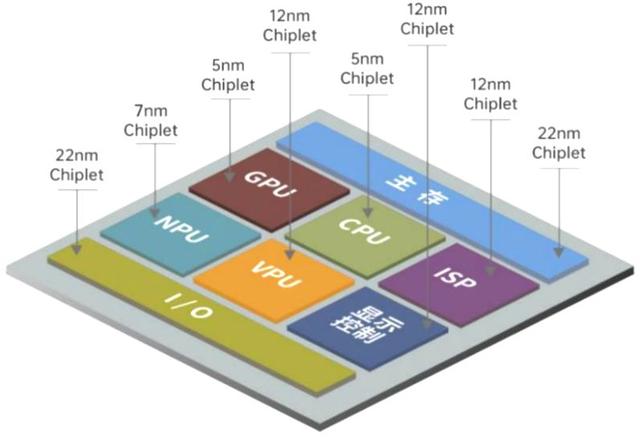

图片来源:芯原

Chiplet出现离不开的趋势:异构集成+高速互联

1.计算机系统的异构、集成程度越来越高

伴随着计算机在人类现代生活中承担越来越多的处理工作,计算机体系结构的异构趋势会愈发明显,需要的芯片面积也会越来越大,同时也需要如电源管理 IC 等芯片与逻辑 芯片异质集成,而 SoC 作为一颗单独的芯片,其面积和加工方式却是受限的,所以 SoC 并不是异构的终极解决方案。

2.芯片间的数据通路带宽、延迟问题得到了产业界的解决

芯片的工作是执行指令,处理数据,芯片间的互联需要巨大的带宽和超低的延时。既然单颗芯片的面积不能无限增加,将一颗芯片拆解为多颗芯片,分开制造再封装到一起是一个很自然的想法。芯片间的互联需要构建强大的数据通路,即超高的频率、超大的带宽、超低的延时,以台积电 CoWoS 技术为代表的先进封装技术也使之得到了解决。

Chiplet带来的机会

国内先进制程发展受阻,Chiplet有望成为国产替代突破口。全球半导体产业博弈升级,国内晶圆厂在先进制程升级上受限。近期《小芯片接口总线技术要求》标准发布,这是中国首个原生Chiplet技术标准,有助于行业规范化、标准化发展,为赋能集成电路产业打破先进制程限制因素,提升中国集成电路产业综合竞争力,加速产业进程发展提供指导和支持。

随着Chiplet小芯片技术的发展以及国产化替代进程的加速,在先进制程受到国外限制情况下,Chiplet为国产替代开辟了新思路,有望成为我国集成电路产业逆境中的突破口之一。