时间:2023-08-31 16:13

人气:

作者:admin

碳化硅(SiC)作为第三代半导体材料, 具有高击穿场强、高饱和电子漂移速率、高热导率、强化学稳定性等优良特性,在电动汽车、轨道交通、高压输变电、光伏、5G 通讯等领域具有重大应用价值。在新能源产业强劲需求下,全球 SiC 产业步入高速成长期,推升了对 SiC 衬底产能的需求。目前商用 SiC 衬底尺寸仍以 6 英寸为主,扩大 SiC 衬底尺寸是增加产能供给、降低成本的重要途径之一。

近年来 SiC 衬底厂商加速推进 8 英寸衬底的研发和量产进度,以抢占 8 英寸先机。行业龙头美国Wolfspeed 最早在 2015 年展示了 8 英寸 SiC 样品,2022 年 4 月,Wolfspeed 启动了全球首家 8 英寸 SiC晶圆厂。虽然起步时间相对于国外较晚,国内 8 英寸 SiC 衬底研究近年来取得了显著进展,2022 年多家单位公布 8 英寸导电型 4H-SiC 产品开发成功,包括山东大学、广州南砂晶圆、中科院物理研究所、山东天岳先进、山西烁科晶体、北京天科合达等单位。

8 英寸与 6 英寸 SiC 晶圆的制造工艺有很大差别,当尺寸扩展到 8 英寸之后,热应力增大,缺陷控制更加困难,尤其是位错缺陷的控制与 6 英寸相比还有一定差距。

目前商用 6 英寸导电型 4H-SiC衬底的 TSD 密度控制在 200 cm-2 以下,优值小于 50cm-2,BPD 密度在 800 cm-2 以下,优值小于 500 cm-2。8 英寸 SiC 衬底要实现量产,提升市场份额,需要进一步降低位错缺陷密度,达到 6 英寸 SiC 衬底的位错缺陷水平,尤其是对器件性能影响较大的TSD 和 BPD。

近期,山东大学与南砂晶圆半导体技术有限公司在8英寸SiC衬底位错缺陷控制方面取得了重大突破,使用物理气相传输法实现了近“零螺位错(TSD)”密度和低基平面位错(BPD)密度的8英寸导电型4H-SiC单晶衬底制备,其中螺位错密度为0.55 cm-2,基平面位错密度为202 cm-2。

并以“低位错密度 8 英寸导电型碳化硅单晶衬底制备(Fabrication of 8-inch N-type 4H-SiC Single Crystal Substrate with Low Dislocation Density)”为题在《无机材料学报》发表(DOI: 10.15541/jim20230325)。

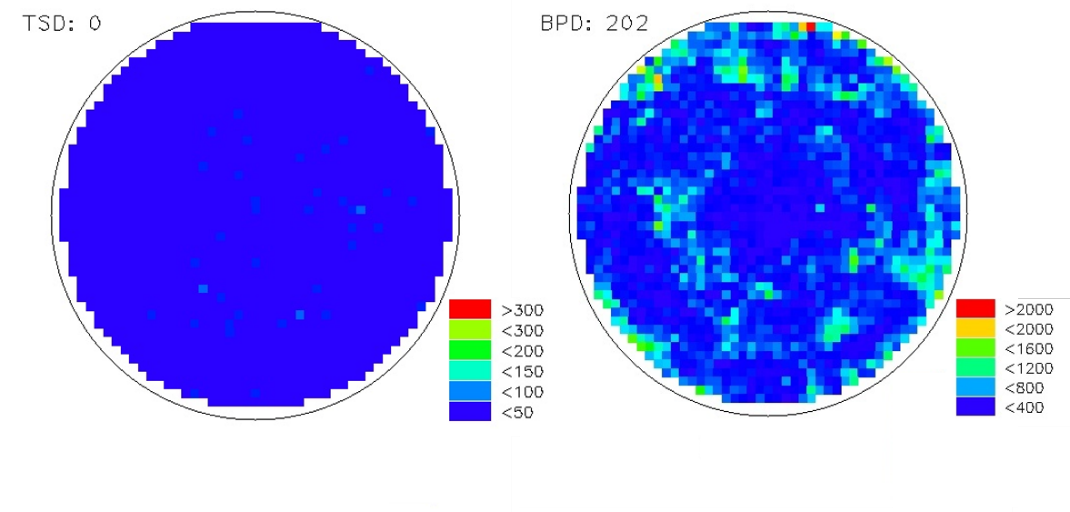

8英寸导电型4H-SiC单晶衬底的螺位错和基平面位错密度及其分布

为制备的 8 英寸导电型 4H-SiC 单晶衬底,使用熔融 KOH 对衬底进行选择性蚀刻,统计 BPD 和TSD 对应的特征腐蚀坑数量,计算 BPD 和 TSD 密度。为衬底的 BPD 密度分布图,平均 BPD密度为 202 cm-2。上图给出了 TSD 密度分布图,平均 TSD 密度<1 cm-2。为不同尺寸 TSD 腐蚀坑对应的数量,其中 TSD 数量总计 42 个,测试点数 1564 个,每个点对应面积 0.0489 cm2,因此TSD 密度=42/(1564×0.0489cm2)=0.55 cm-2。

研究团队实现了近“零 TSD”和低 BPD 密度的 8 英寸导电型 4H-SiC 单晶衬底制备,8 英寸 SiC 单晶衬底位错缺陷的有效控制,有助于加快国产 8 英寸导电型4H-SiC 衬底的产业化进程,提升市场竞争力。

作者:(熊希希,杨祥龙,陈秀芳,李晓蒙 ,谢雪健 ,胡国杰 ,彭燕 ,胡小波 ,徐现刚 )山东大学 晶体材料国家重点实验室,新一代半导体材料研究院;(于国建,王垚浩 )广州南砂晶圆半导体技术有限公司

审核编辑:刘清