时间:2013-04-08 11:08

人气:

作者:admin

电子发烧友网核心提示:Cadence FPGA System Planner(FSP)是一款完整性高的FPGA-PCB系统化协同设计工具。此次主要为大家介绍FPGA System Planner的基本情况,详见原文。

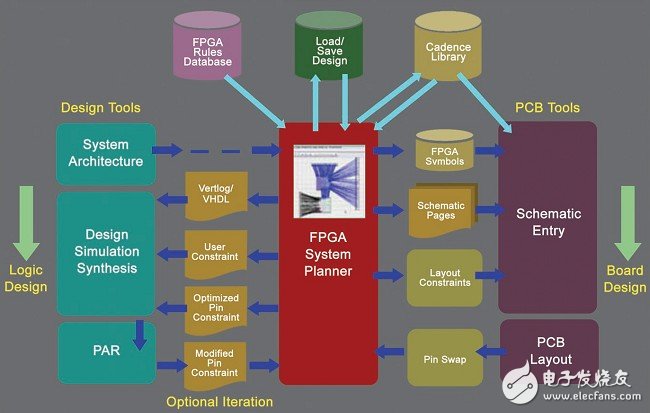

在较新的FPGA设计中几乎有超过千个可编程的I/O引脚,若再包含多个FPGA时,工程师就会遇到初期规划I/O引脚,并配合后期layout placement时该如何最佳化的瓶颈及困难。Cadence OrCAD and Allegro FPGA System Planner便可满足较复杂的设计及在设计初级产生最佳的I/O引脚规划,并可透过FSP做系统化的设计规划,同时整合logic、schematic、PCB同步规划单个或多个FPGA pin的最佳化及layout placement,借由整合式的界面以减少重复在design及PCB Layout的测试及修正的过程及沟通时间,甚至透过最佳化的pin mapping、placement后可节省更多的走线空间或叠构,FSP不仅能加快产品上市时间,还能够节省设计成本。

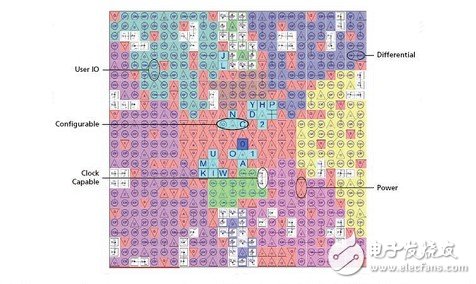

图1 完整性高的FPGA-PCB系统化协同设计工具

Specifying Design Intent

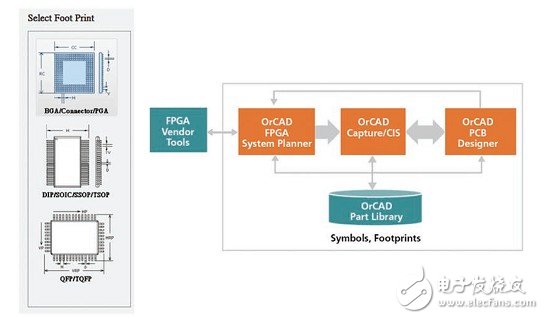

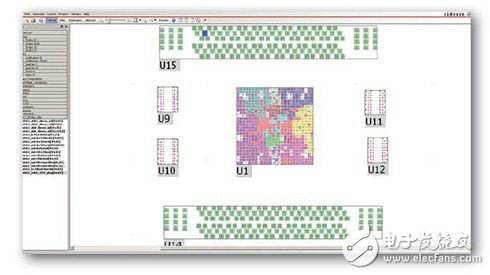

在FSP整合工具内可直接由零件库选取要摆放的零件,而这些零件可直接使用PCB内的包装,预先让我们同步规划FPGA设计及在PCB的placement。

在设计方面,客户可直接定义FPGA及其他零件的连线关系,节省在其他工具设计再转入Schematic、PCB的时间,以目前常应用的DDR2、DDR3、PCI Express设计,皆可透过FSP产生FPGA和memory DIMM或多个FPGA间的连线关系。

FPGA Device Rules

FSP的library内包含FPGA models,明定了FPGA vendor 提供的pin脚位的位置及电气特性。