时间:2023-08-02 14:43

人气:

作者:admin

2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自主研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

我们EDA探索频道,今天迎来了第25期的内容——Intel的工艺历史,下面就跟着小编一起来开启今天的探索之旅吧~

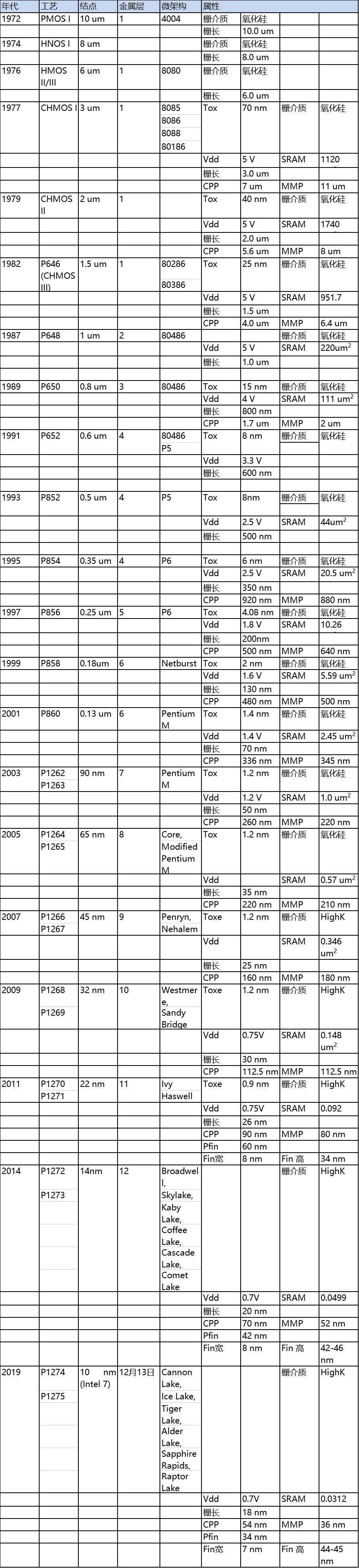

下表显示了英特尔集成电路工艺发展的历史。数值取自英特尔的各种文件,包括 IDF 演示文稿、ISSCC 文件和 IEDM 文件。需要注意的是,虽然我们做了大量工作尽量保证数值的准确,但英特尔公司自己文件中的某些数字仍有细微差别,因此可能存在差异。SRAM bitcell是高密度 6T bitcell,但在最初的几个工艺中使用了较小的bitcell设计。此外,金属层数是指消费类芯片(例如消费类手机和台式机)的金属层数;服务器型号使用的金属层数要多得多。最后,从 45 纳米节点开始,英特尔转而使用高κ材料,因此显示的氧化物厚度指的是等效氧化物厚度。

术语

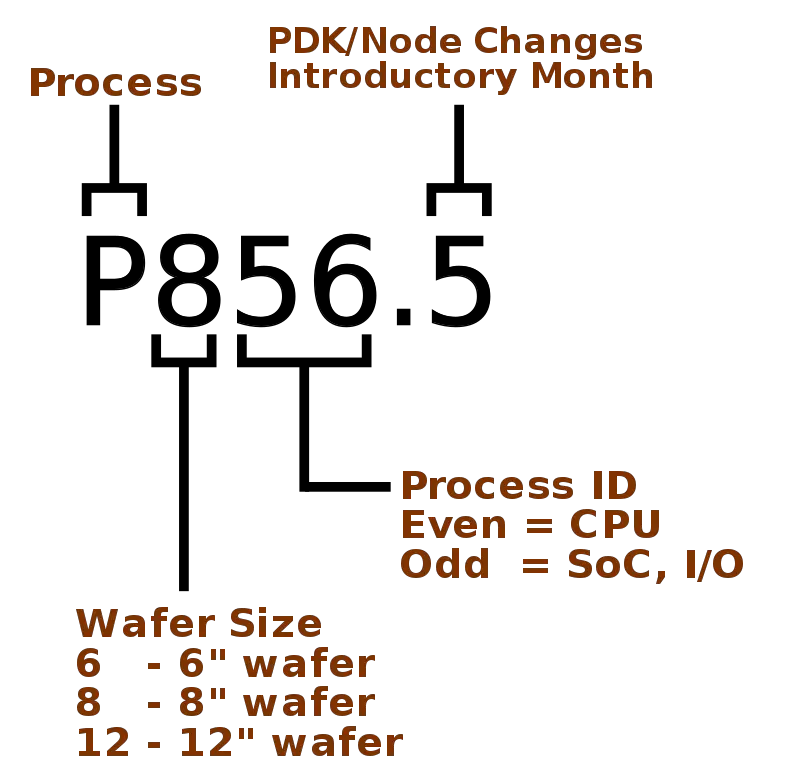

几十年来,英特尔一直使用相同的命名方案。所有工艺技术(包括封装技术)都以 "P "开头,然后是晶圆尺寸和工艺 ID。一般来说,工艺 ID 是一个自动递增值,奇数值通常保留给 SoC 和 I/O(低功耗)设备,而偶数值则用于英特尔的高性能处理器产品线。

△点击查看大图

SRAM微缩

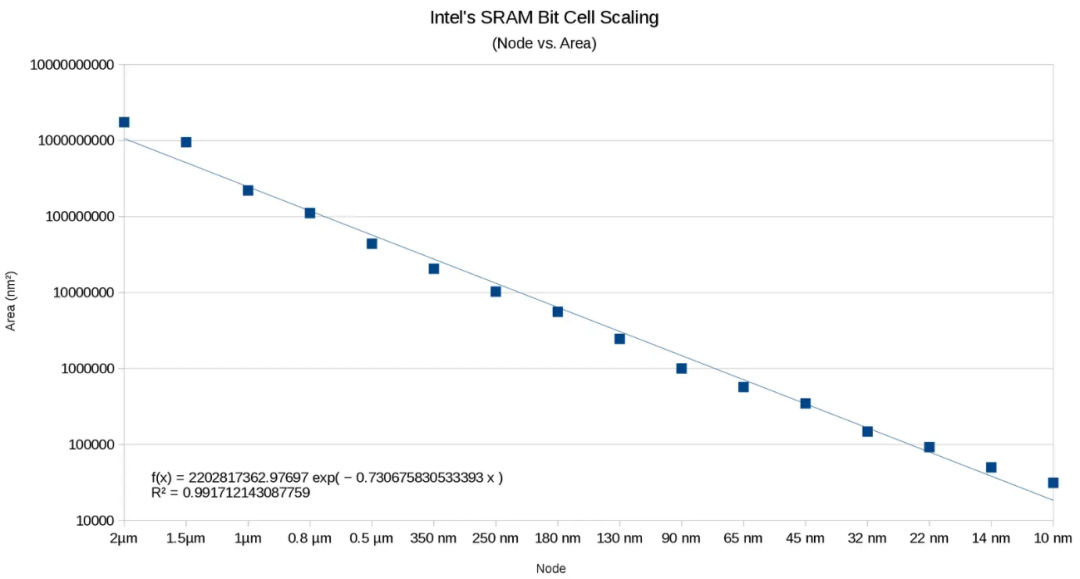

就英特尔而言,从 2 um到 10 nm,SRAM 6T 位单元平均缩小了 0.496 倍,以遵循摩尔定律密度翻倍要求。实际上在 65 nm工艺节点之前,SRAM 的收缩幅度更大。还应注意的是,逻辑通常比典型的 6T SRAM 单元微缩更容易,因此随着时间的推移,原始逻辑密度扩展得更大。不过,SRAM 的大小可能是典型逻辑单元密度的三到四倍。

编辑:黄飞