时间:2023-08-11 17:33

人气:

作者:admin

进入2010年代后,线宽接近原子的尺寸,微细化的速度开始放缓;随着前沿制造技术的使用成本越来越高,设计方法正在转向多芯片模块。

在此情况下,受到关注的是将多枚芯片纵向堆叠的3D以及横向排列连接的技术,并且可以不依赖微细化提高半导体的功能。

或许,在未来的几年里,多芯片系统封装(SiPs)预计将变得更加广泛,先进的 2.5D 和 3D 芯片封装技术将变得更加重要。

目前,由于摩尔定律的限制,在提高芯片性能的方向上,研发人员开辟了另外一个新的路径:即利用3D技术通过有效堆叠多个芯片来提高半导体的综合性能。

有持续关注奇普乐文章的半导体从业者,或许都知道:2022年我们写了关于台积电的核心技术CoWoS、InFO。

图片来自:台积电

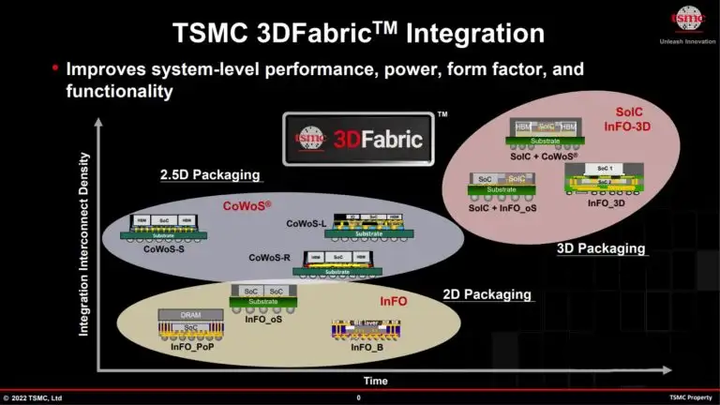

在此背景下,本次将带大家深入了解台积电先进封装技术,台积电 3DFabric 是 3D 硅堆叠和先进封装技术的关键组成:

6月8日,台积电宣布先进后端六厂(Advanced Backend Fab 6)正式启用,采用3DFabric技术,为系统集成技术的量产做好准备。

3DFabric是一个具有极大潜力的技术方向,台积电率先全球同行建造了首间使用该技术的工厂,意在夺取芯片市场上更多前沿技术产品的订单。

首先我们要知道:

其次,在 3D 硅堆叠部分,台积电正在 TSMC-SoIC 系列中添加基于微凸点的 SoIC-P,以支持更多对成本敏感的应用。

图片来自:台积电

所以,2.5D CoWoS 平台可为人工智能、机器学习和数据中心等 HPC 应用集成高级逻辑和高带宽内存;InFO PoP 和 InFO-3D 支持移动应用,InFO-2.5D 支持 HPC chiplet 集成。

另外,SoIC 堆叠芯片可以集成到 InFO 或 CoWoS 封装中,以实现最终系统集成。

于是乎,台积电3D 硅堆叠技术,可追溯到2018年....

2018年4月的美国加州圣塔克拉拉(Santa Clara)第二十四届年度技术研讨会上,台积电首度对外界公布创新的系统整合单芯片(SoIC)多芯片3D堆叠技术;这在当时被誉为可再次把三星狠狠甩在后头、实现3D IC的高阶封装技术。

尤其,与传统的二维芯片把所有的模块放在平面层相比,三维芯片允许多层堆叠,而TSV是用来提供多个晶片垂直方向的通信;且,TSV是3D芯片堆叠技术的关键。

图片为:3D芯片堆叠结构示意图

与此同时,其3D硅堆叠技术不仅如此:

SoIC-P 基于 18-25μm 间距 μbump 堆叠,适用于对成本更敏感的应用,如移动、物联网、客户端等。

SoIC-X 基于无扰动堆叠,主要针对 HPC 应用。其晶圆上芯片堆叠方案具有 4.5 至 9μm 键距,并已在 TSMC 用于 HPC 应用的 N7 技术上量产。

SoIC 堆叠芯片可以进一步集成到 CoWoS、InFo 或传统的倒装芯片封装中,用于客户的最终产品。

小芯片堆叠是提高芯片性能和成本效益的关键技术,紧接着来了解一下SoIC技术:

SoIC技术是采用硅穿孔(TSV)技术,可以达到无凸起的键合结构,可以把很多不同性质的临近芯片整合在一起;能直接透过微小的孔隙沟通多层的芯片,达成在相同的体积增加多倍以上的性能。

图片来自:台积电

SoIC技术为芯片 I/O 提供了强大的键合间距可扩展性,从而实现高密度芯片间互连。键距从低于 10 µm 的规则开始;与当前业界最先进的封装解决方案相比,短芯片到芯片连接具有更小的外形尺寸、更高的带宽、更好的电源完整性 (PI)、信号完整性 (SI) 和更低的功耗。

SoIC 技术将同构和异构小芯片集成到单个类似 SoC 的芯片中,该芯片具有更小的占地面积和更薄的外形,可以整体集成到先进的 WLSI(又名 CoWoS 服务和 InFO)中;从外观上看,新集成的芯片就像通用的SoC芯片一样,但嵌入了所需的异构集成功能。

值得一提的是:如果将各种芯片结合起来的3D技术得到普及,专注于设计的无厂半导体厂商之间、以及与后工序代工企业等的合作将提高重要性。

综上所述,随着物联网、5G通信、人工智能、大数据等新技术的不断成熟,全球集成电路行业进入新一轮的上升周期,封测行业受益市场规模持续增长。

据 Yole 数据统计,2021 年全球先进封装市场规模约 350 亿 美元,预计到 2025 年先进封装的全球市场规模将达到 420 亿美元,2019-2025 年全球先进封装市场规模 CAGR 约 8%,增速高于传统封装市场。

审核编辑:刘清