时间:2025-08-05 14:02

人气:

作者:admin

第13章

CGC——时钟控制

CGC

CGC(Clock Generation Circuit):时钟生成电路

13.1

CGC模块简介

#CGC全称是Clock Generation Circuit,中文译为“时钟生成电路”,或者也可以叫它“时钟控制电路”。

13.1.1

时钟源

我们学过《数字逻辑电路》知道,在芯片集成电路的系统中,必须要输入时钟信号进行驱动,才能使得这些逻辑电路正常工作。那么系统所需的这些时钟信号是来源于哪里的呢?

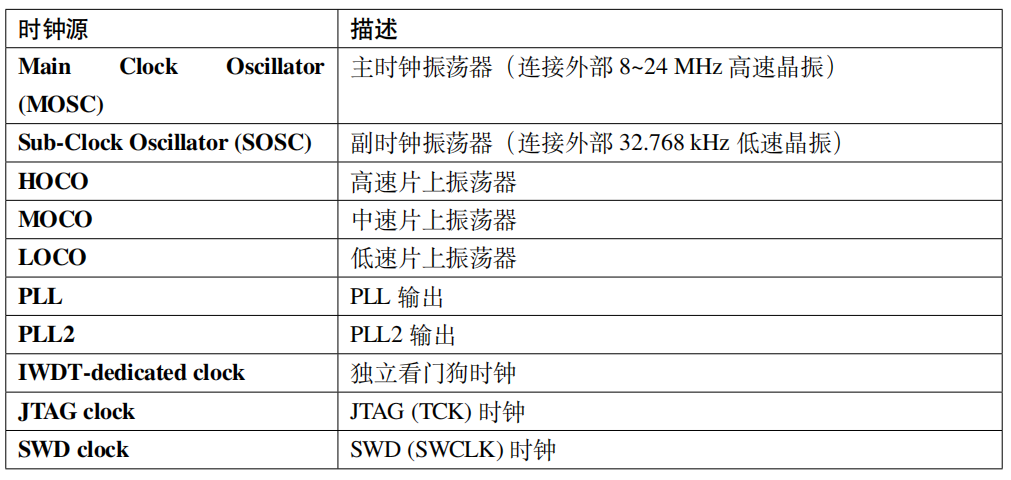

时钟信号的来源我们称之为时钟源。RA6M5/RA4M2的时钟源如下表所示:

表1:RA6M5/RA4M2时钟源

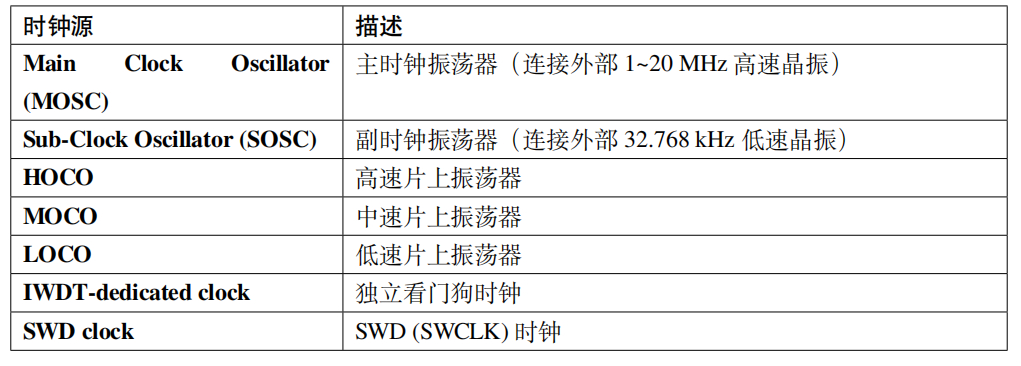

RA2L1的时钟源如下表所示:

表2:RA2L1时钟源

相关概念的详细说明:

Main Clock Oscillator(MOSC):

主时钟振荡器

RA6M5/RA4M2连接外部8 ~ 24 MHz高速晶振(连接引脚EXTAL、XTAL);

RA2L1连接外部1 ~ 20 MHz高速晶振(连接引脚EXTAL、XTAL)。

Sub-Clock Oscillator(SOSC):

副时钟振荡器

连接外部32.768 kHz低速晶振(连接引脚XCIN、XCOUT)。

32.768 kHz的外部时钟频率一般是用于RTC为用户系统提供时间日历功能的。

Phase Locked Loop(PLL、PLL2):

PLL即锁相环。

PLL电路具有倍增振荡器频率的功能,可选择输入到PLL的时钟信号,并对其进行分频和倍频,输入时钟源为MOSC、HOCO,输入频率8 MHz至24 MHz,倍频比可在10到30之间选择(0.5 步进)

PLL输出频率:120 MHz ~ 200 MHz。

PLL2输出频率:120 MHz ~ 240 MHz。

注:RA2L1没有PLL,因此它的主频(48 MHz)相对比较低,而这也有利于低功耗。

High-speed on-chip oscillator

(HOCO):高速片上振荡器

振荡频率:RA6M5/RA4M2的为16/18/20 MHz

振荡频率:RA2L1的为24/32/48/64 MHz

Middle-speed on-chip oscillator

(MOCO):中速片上振荡器

振荡频率:8 MHz

Low-speed on-chip oscillator

(LOCO):低速片上振荡器

振荡频率:32.768 kHz

IWDT-dedicated clock(IWDTLOCO):

IWDT专用片上振荡器

振荡频率:15 kHz

External clock input for JTAG(TCK):

JTAG的外部时钟输入

振荡频率:最大25 MHz

注:RA2L1是不支持JTag接口的。

External clock input for SWD

(SWCLK):SWD的外部时钟输入

振荡频率:RA6M5/RA4M2的最大25 MHz

振荡频率:RA2L1的最大12.5 MHz

13.1.2

模块输入时钟

上述内容我们知道已经有了各个时钟源的输入,那么,输入的各个时钟源是要输出时钟信号给到各个时钟线上的,而芯片的各种模块又挂载到各个时钟线上。

系统中的每一个模块都需要不同的工作频率,对应到各个时钟线所能提供的最大时钟频率也有快有慢,而不是完全一样。用户在使用一些外设或模块时需要特别考虑其输入时钟频率,这可以通过配置对应时钟线的时钟频率来满足不同模块的需求。

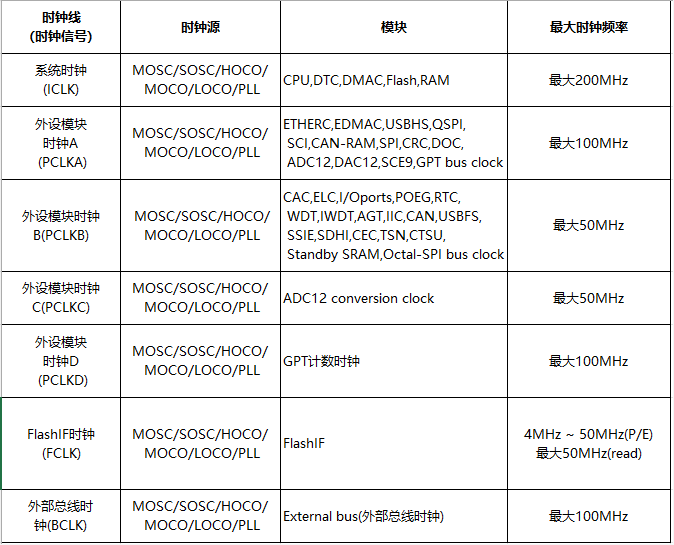

以RA6M5为例,下面是系统内部主要时钟线的时钟源及其用以支持的模块和其所能提供的最高频率。

表3:RA6M5内部时钟说明

注意到设置时钟频率的一些限制:

ICLK ≥ PCLKA ≥ PCLKB,PCLKD ≥ PCLKA ≥ PCLKB

ICLK ≥ FCLK,ICLK ≥ BCLK

13.1.3

时钟相关的引脚

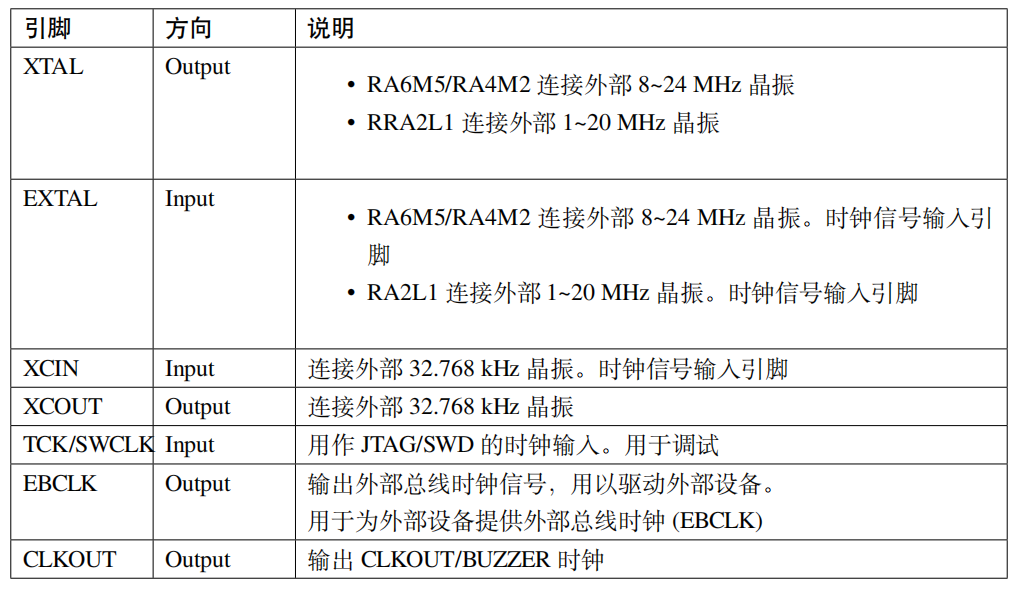

与时钟相关的#引脚及其说明如下表所示。

表4:时钟相关的引脚