时间:2025-02-13 19:34

人气:

作者:admin

PCB的布局和走线在射频电路中占据举足轻重的作用,影响整个PCB的设计性能,甚至是整个产品的性能。在绘制完成原理图后,开始绘制PCB前,首先要确认绘制的PCB是几层板子,射频一般建议是4层,第二层保持完整的GND,其次再确定整体布局,再开始走线,确认线宽。

PCB布局一般原则

1、元器件布局时尽量单面放置,可以降低产品生产时的加工成本。

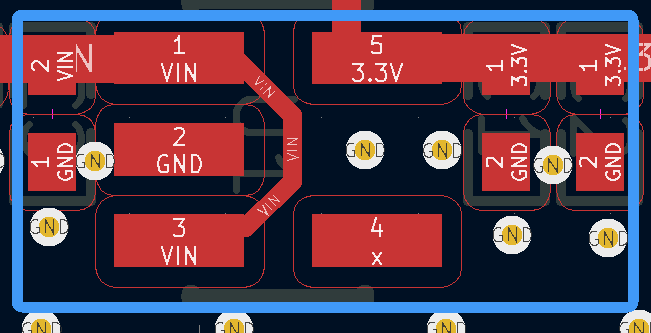

2、封装、结构相类似的电路,采用对称结构布局,有电气关系的器件尽量放在一起,器件要做到模块化。

对称结果布局

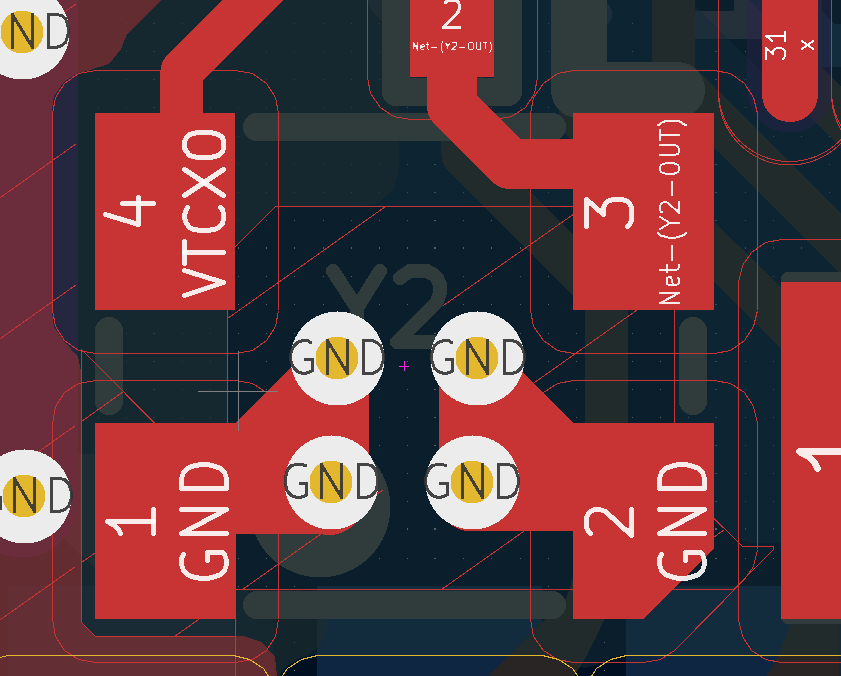

3、在高频率的数字电路中,晶振(有源)和晶体(无源)需要尽可能的靠近芯片,如果离芯片太远,芯片接收到信号后产生的方波会受到一定干扰,可能会导致数字电路工作异常。

4、接口器件的布局要合理化,元器件放置要考虑到板边的距离是否合理,例如直插的USB端子,如果布局时离板边过远会出现直插器件插不进板子的情况,见下图,放置到板子中心,直插的USB根本无法插入。

5、对于一些接口器件要标明”+”、”-”,做出丝印说明,防止因为接线错误导致电路板子烧毁。

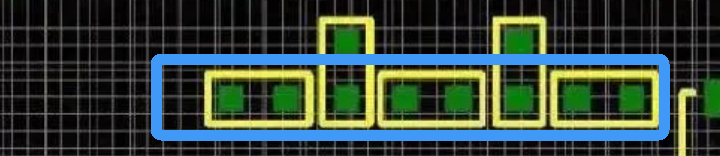

6、对于射频模组,优先布局射频电路,对于Π形网络,尽量呈现“一字形“,而且两边要铺GND处理,见下图。

7、高压器件和低压器件要保持安全距离,一般压差100V,相隔开1毫米。高压和低压之间也可以通过隔开地处理。这样的目的是电器绝缘。

8、滤波电容和去耦电容要放置在芯片的入口处和芯片出口。放置去耦电容和滤波电容是为了改善电源的质量,提高抗干扰的一种手段。放置电容时紧靠芯片。

9、布局时对于对热量敏感的元器件要远离发热量大的器件,发热量大的器件背面要做到开窗散热,或者安装散热片。

10、布局时,还需要考虑是否方便焊接,大器件旁边避免放置小器件,需要调试的器件因为需要经常焊接,要预留够足够的空间,避免拆去器件困难。

PCB走线一般原则

1、走线3W原则,3W原则指的是:线的中心间距不小于3倍线宽,从而降低走线之间的干扰,走线避免直角。

2、走线时,电源线和地线要尽量粗。减小压降,以及走线过细可能会导致PCB的走线被烧断。3、晶振走线要短,尽量避免打过孔换层,包地处理。晶振下面尽量避免走电源线、信号线,PCB同层挖空打过地过孔到第二层,如下图:

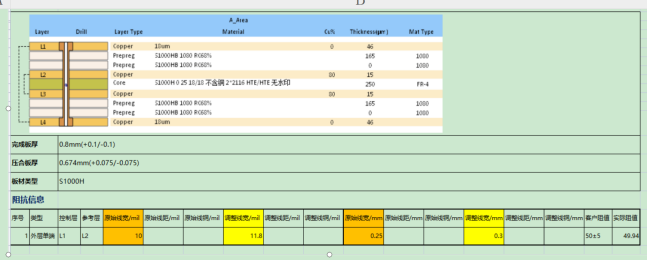

4、射频走线要做阻抗设计,可以通过软件SI9000,在板厚和到地的间距确认下计算线宽,见下图:

5、差分走线

差分走线相对于单端走线,抗干扰能力强,抑制EMI,差分线走线要做到等宽等间距。

*部分资料和图片来源于网络,侵删