时间:2024-08-05 14:58

人气:

作者:admin

Altium Designer 24.7.2

发布时间:2024年7月23日

Altium Designer 24.7.2离线包

15天免费试用 Altium Designer

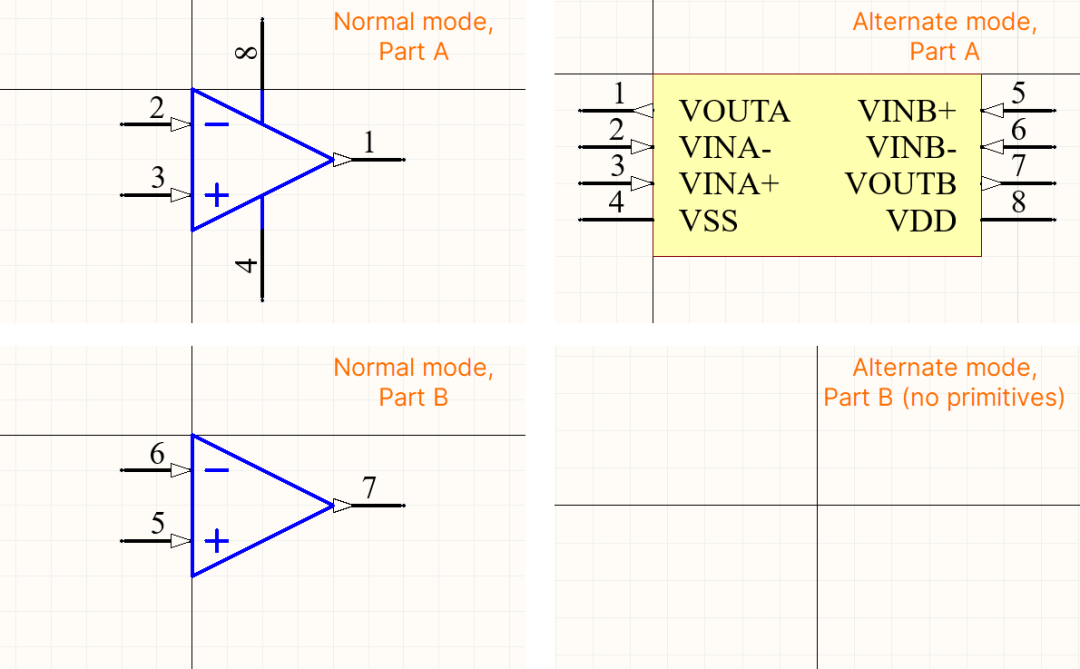

原理图输入改进 多部件元件增强 如果多部件元件仅在一个子部件中定义了基元,则当该子部件被放置在原理图图纸上时,位号标识符后缀现在将被隐藏。此项功能仅适用于备用显示模式;对于Normal显示模式,后缀将始终显示。此外,当某个子部件/模式不含基元时,同样将无法再选定该子部件(或备用显示模式)。

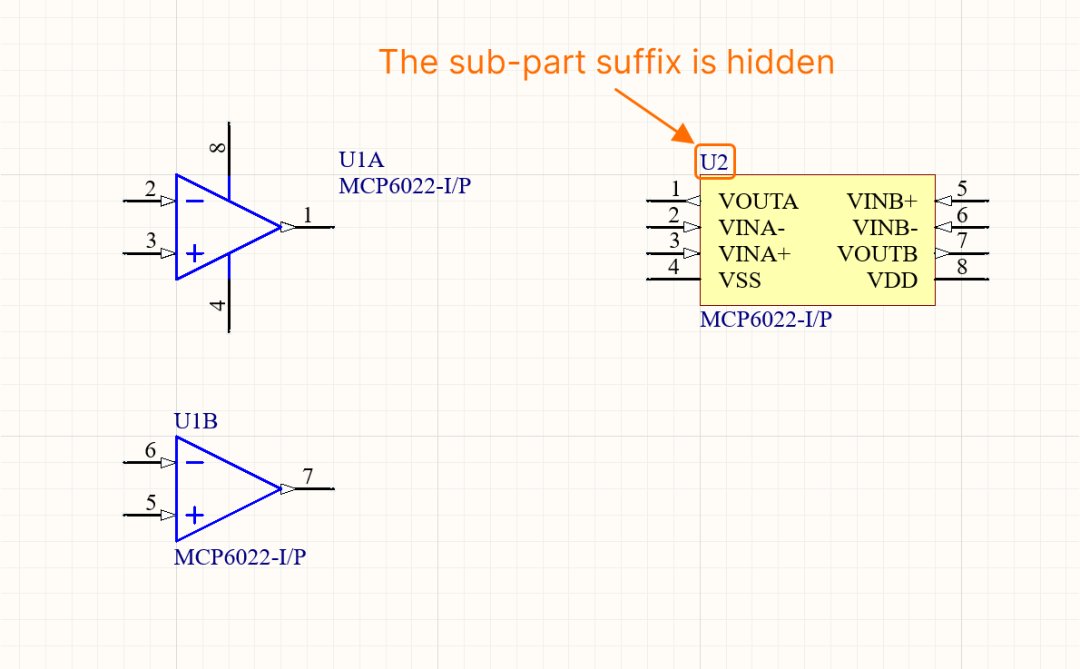

双运算放大器元件的原理图符号示例。在正常模式下,将以两个子部件表示元件。而在备用模式,将以单个子部件表示元件。

在原理图图纸上,如果子部件是所选备用模式中的唯一子部件,则该子部件的位号标识符后缀将不会显示。

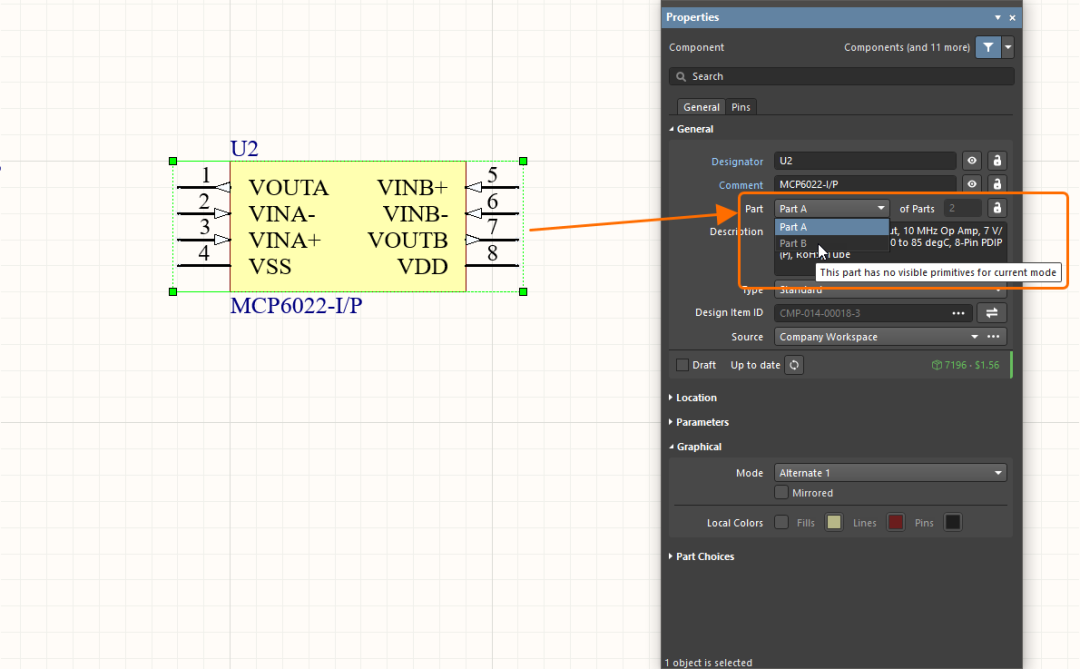

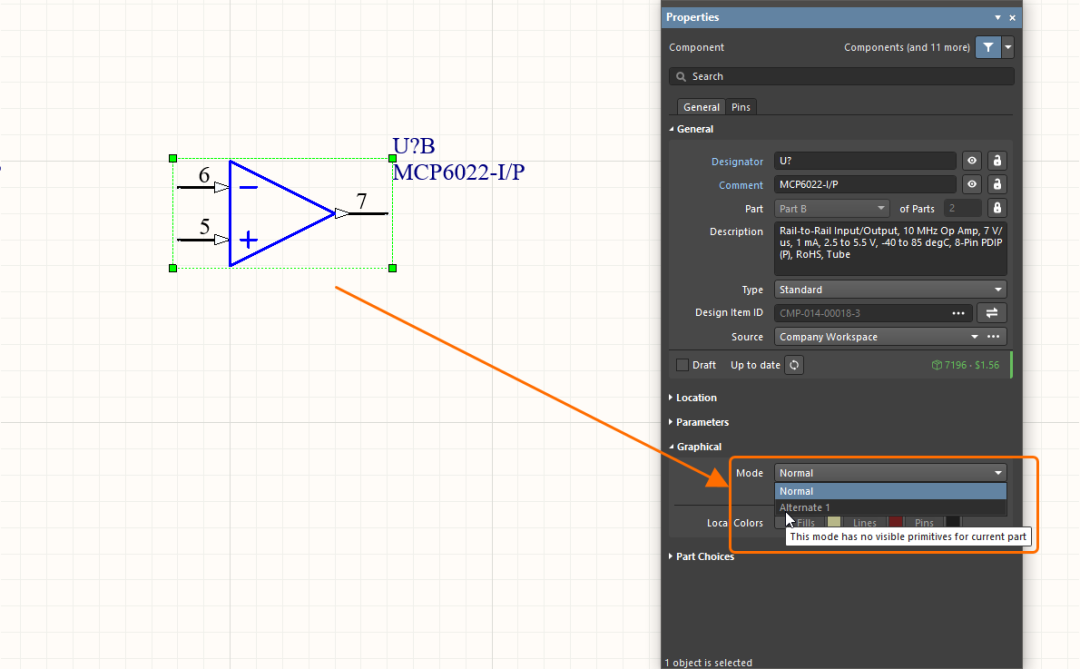

当某个子部件不含基元时,将无法再选定该子部件。

当某个备用显示模式不含基元时,将无法再选定该模式。 如需了解更多信息,请参阅Creating a Schematic Symbol页面。

添加了新的端口违规

在Project Options对话框Error Reporting选项卡Violations Associated with Nets类别中,添加了一种新的违规类型,用于检测在任何源原理图文档中不含对应/匹配端口的平行式设计端口。当不含匹配端口或端口未连接时,将发生Port with No Matching Ports错误违规。默认违规状态为No Report。 仅当Project Options对话框Options选项卡上的Net Identifier Scope选项被设置为Flat(仅端口为全局模式)或Global(网络标签和端口均为全局模式)时,才会检测到此违规类型。

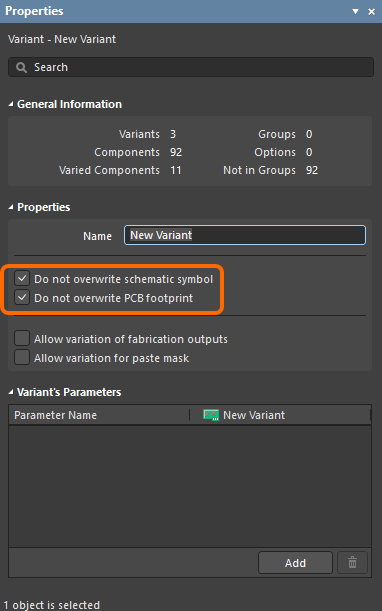

如需了解更多信息,请参阅Verifying Your Design Project页面。 能够保持备用零件的符号/封装不变 您现在无需更改原理图上的符号或向PCB添加封装,即可选择备用零件。在Properties面板中,根据需要启用Do Not Overwrite Schematic Symbol和/或Do Not Overwrite PCB Footprint选项,如下图所示。所选备用零件的参数会如实地显示在ActiveBOM中。

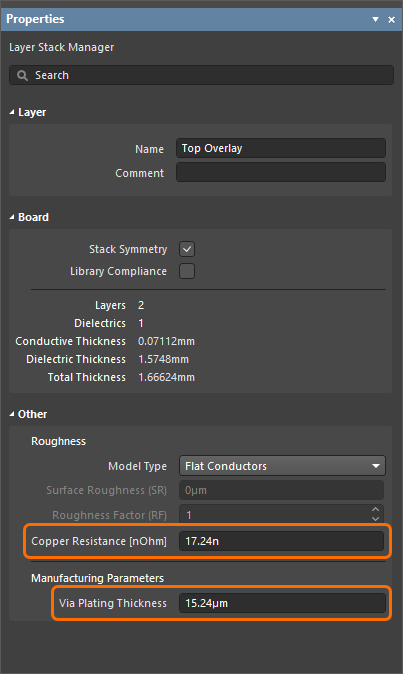

如需了解更多信息,请参阅Working with the Variant Manager页面。 PCB设计改进 在层堆栈管理器中添加了其他选项 在Layer Stack Manager Properties面板中,添加了一些对Power Integrity仿真非常重要的关键参数。可使用Properties面板,将Copper Resistance和Via Plating Thickness作为电路板层堆栈属性的一部分进行定义。

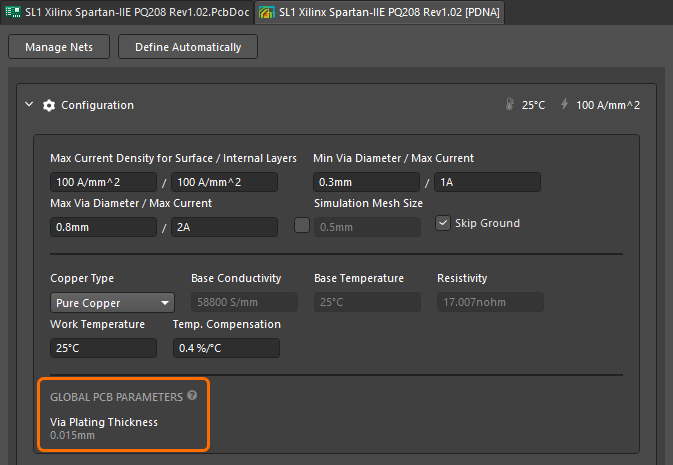

将电路板导出为Ansys EDB格式时,将包含这些参数。Power Analyzer by Keysight工具同样支持Via Plating Thickness参数。该参数的值将显示在分析器文档的Configuration区域中。

如需了解更多信息,请参阅Defining the Layer Stack页面。

回流路径过孔检查(开放测试阶段)

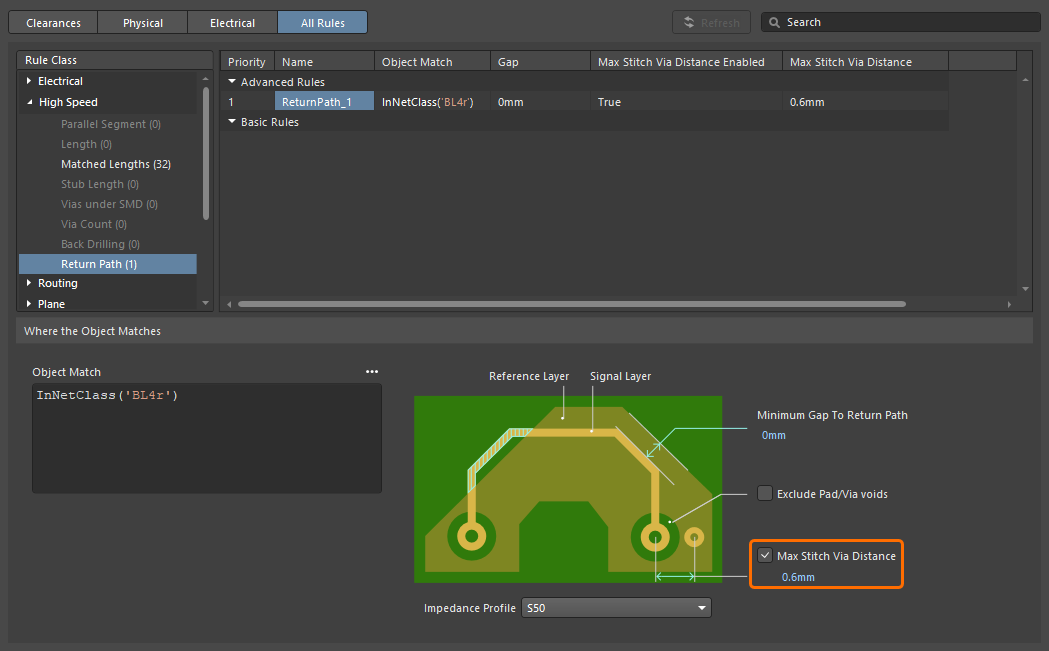

当高速信号从一个参考平面传递到另一个时,回流信号也应该能够通过回流过孔在两个平面之间进行传递。为了检查此类过孔是否存在于信号过孔的特定距离内,已将Return Path规则扩展为包含一个新的Max Stitch Via Distance选项,以确保可使用该选项定义回流路径过孔是否应该存在于示波信号过孔的给定距离(默认值为1.5毫米)内。回流路径过孔应该提供与Layer Stack Manager中定义的参考层的连接,以实现相应的阻抗剖面。

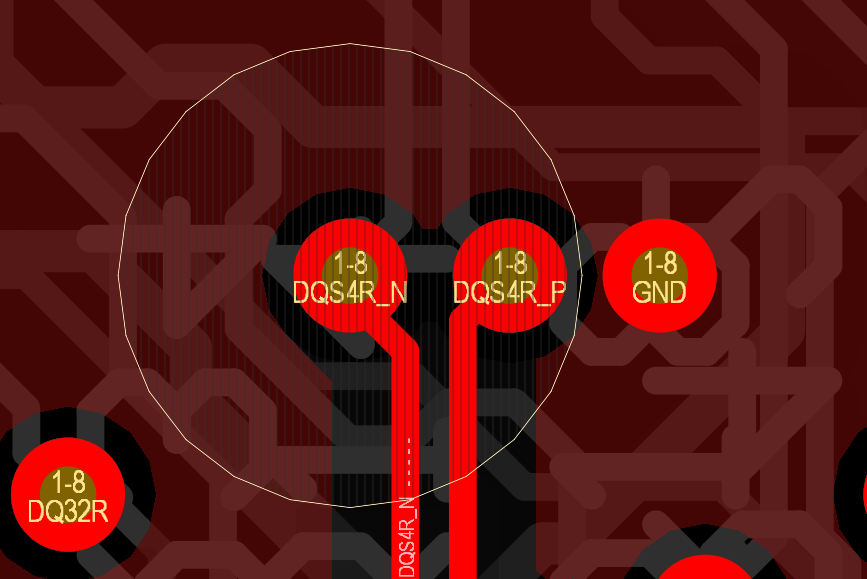

在Constraint Manager中配置的最大缝合孔距离约束示例

在PCB Rules and Constraints Editor对话框中配置的最大缝合孔约束示例 当在规则中启用了Max Stitch Via Distance 选项,并为其定义了非零值时,将在Batch DRC过程中检查指定距离内是否存在回流路径过孔。

最大缝合孔距离约束违规示例。此处网络DQS4R_N的过孔在指定距离处没有回流路径过孔。 此功能处于Open Beta阶段,且仅在Advanced Settings对话框中启用PCB.Rules.CheckReturnPathVia选项时可用。 如需了解更多信息,请参阅High Speed Design页面。 导线环路删除功能增强(开放测试阶段) 在Interactive Router中,引入了一种新的环路自动删除执行方式。此项更新改进了使用Any Angle转角样式进行布线时的环路删除功能,改进了环路删除后的过孔删除功能(见下文),并为将来的增强功能奠定了基础。 环路删除后删除过孔 当存在过孔与焊盘直接连接时,如果在删除环路后认为不再需要过孔,则现在可以将过孔删除(前提是已在Properties面板中启用了Remove Loops With Vias选项,以实现交互式布线)。

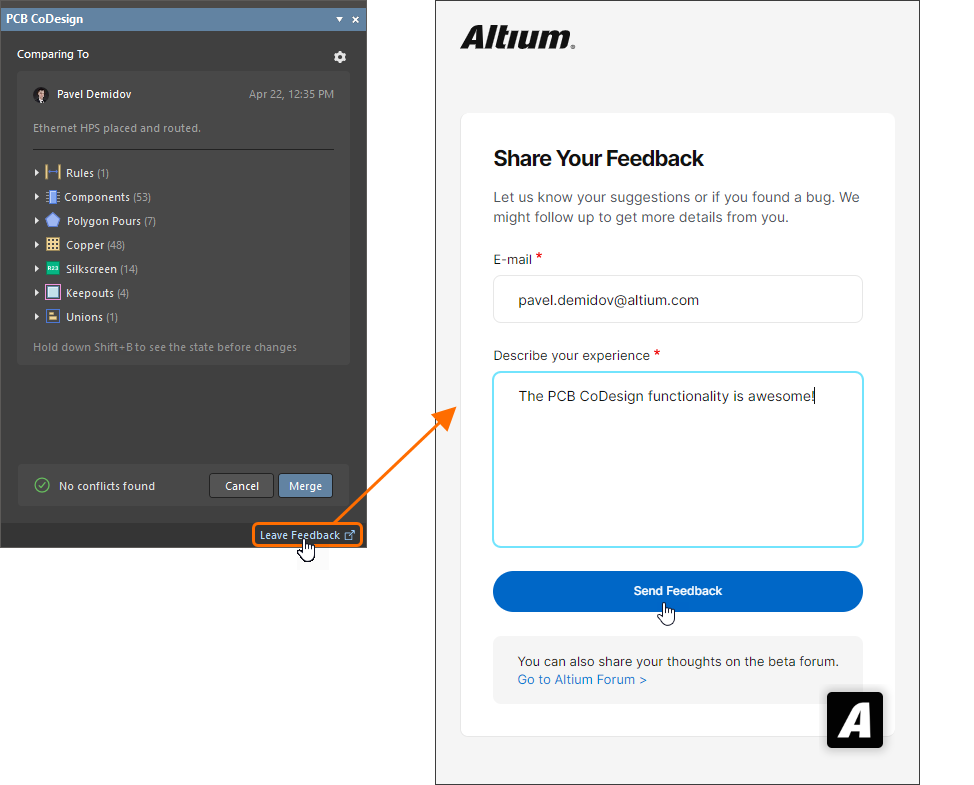

此功能处于Open Beta阶段,且仅在Advanced Settings对话框中禁用了Legacy.PCB.Routing.LoopRemoval选项时可用。 如需了解更多信息,请参阅 Interactive Routing和 Differential Pair Routing页面。 PCB CoDesign改进 添加了在Altium中留下反馈功能 在PCB CoDesign面板中,添加了Leave Feedback控件,以确保您能够直接向Altium Developers发送反馈,并提出仅与PCB CoDesign功能相关的建议或问题。

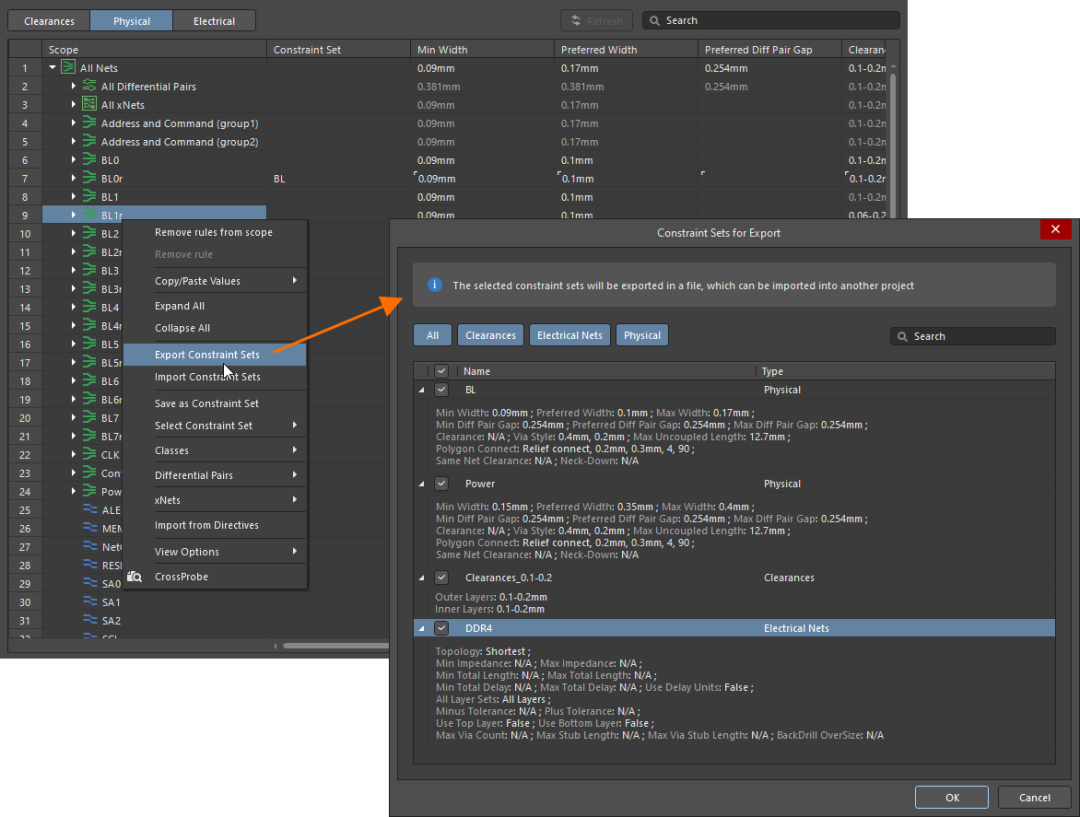

如需了解更多信息,请参阅PCB CoDesign页面。 约束管理器改进 在设计之间导入/导出约束集 此功能将允许您导入和导出约束集,以确保能够在不同电路板设计之间快速复用约束信息。如需访问此项新功能,请在Constraint Manager的Clearances、Physical或Electrical视图中右键单击,然后选定Export Constraint Sets或Import Constraint Sets。

导出约束集

选定Export Constraint Sets后,将打开Constraint Sets for Export对话框,并在栅格内列出设计中当前存在的所有约束集。使用复选框选定想要导出的约束集,然后单击OK按钮。所选约束集将被导出到扩展名为*.CstrDot的文件中。然后,可以将该文件导入到另一个设计中。

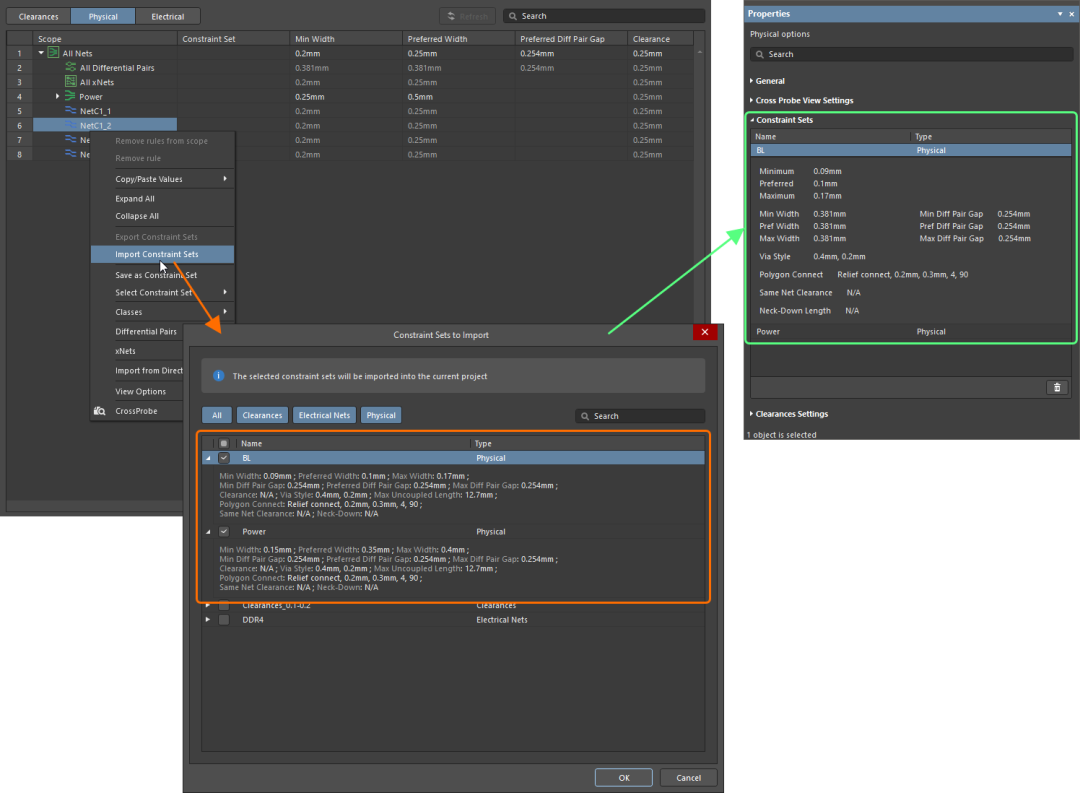

导入约束集 选定Import Constraint Sets后,将打开标准File Explorer对话框,您可以在其中选定一个想要导入的*.CstrDot文件。在打开的Constraint Sets for Import对话框中,选定想要从该文件导入的约束集,然后单击OK按钮。当选定Constraint Manager的相应视图时,可在Properties面板中检查导入的约束集,并且可将其应用于对象。

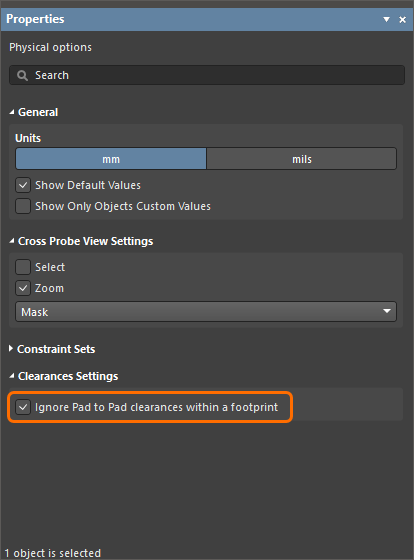

如需了解更多信息,请参阅Defining Design Requirements Using the Constraint Manager页面。 忽略封装内焊盘到焊盘间距的全局选项 您可以通过新的全局选项,指定是否忽略同一元件封装内焊盘之间的间距。当从原理图或PCB访问Constraint Manager时,可在Clearances和Physical视图中使用该选项。在Properties面板的Clearances Settings区域中切换Ignore Pad to Pad Clearances within A Footprint选项,以将该设置应用于所有定义的间距规则。

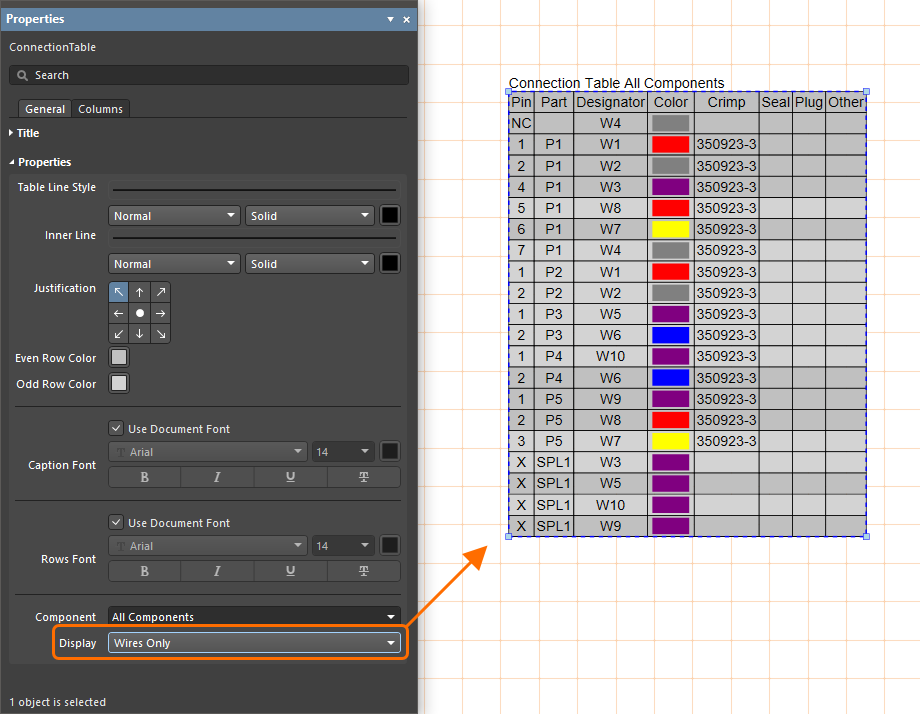

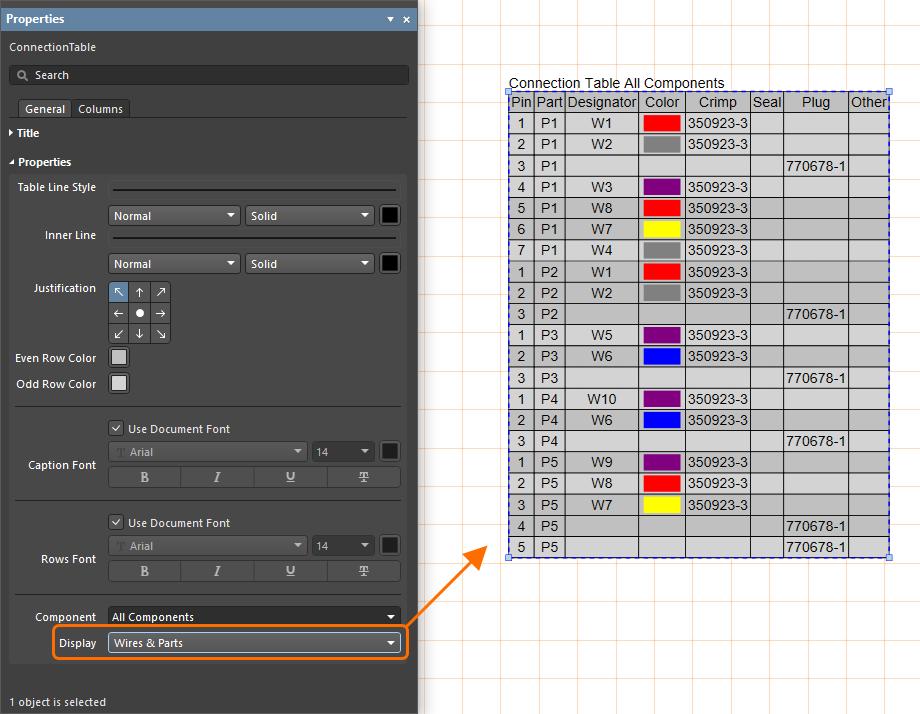

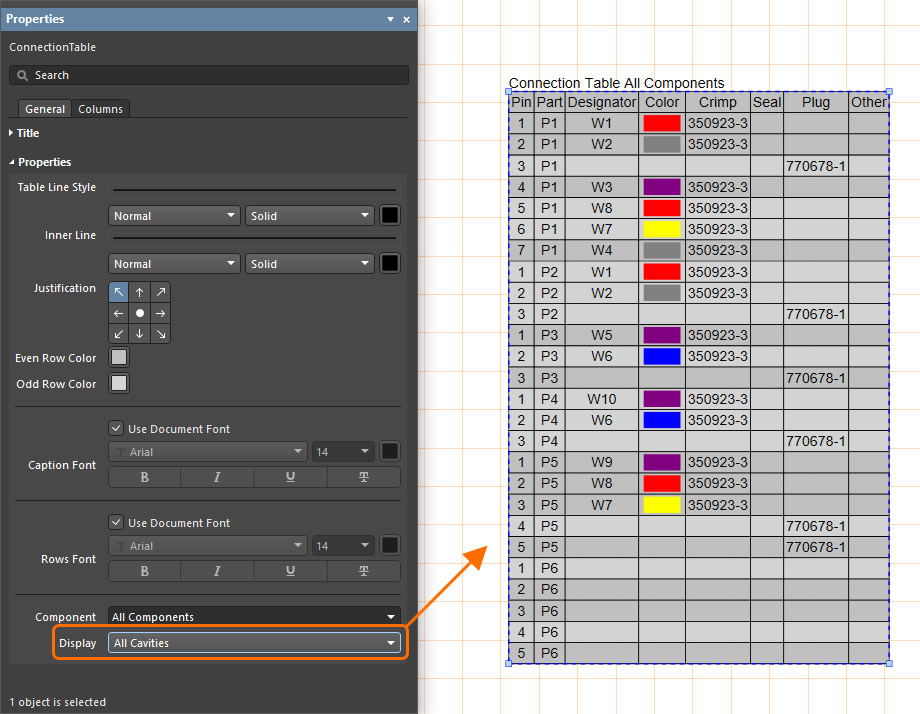

如需了解更多信息,请参阅 Defining Design Requirements Using the Constraint Manager 页面。 线束设计改进 在连接表中显示型腔选项 您现在可以控制Harness Manufacturing文档(*.HarDwf)Connection Table中显示的型腔类型。使用Properties面板中的Display下拉列表,选定想要显示的所需型腔:

Wires Only – 仅显示连接了导线的引脚

Wires & Parts – 显示连接了导线的引脚以及添加了任何型腔零件的引脚,例如在密封连接器不含导线的情况下的插头

All Cavities – 显示所有元件的所有引脚,而不考虑连接的导线和添加的型腔(例如,如果元件具有10引脚,则所有10个引脚均将显示在表中)

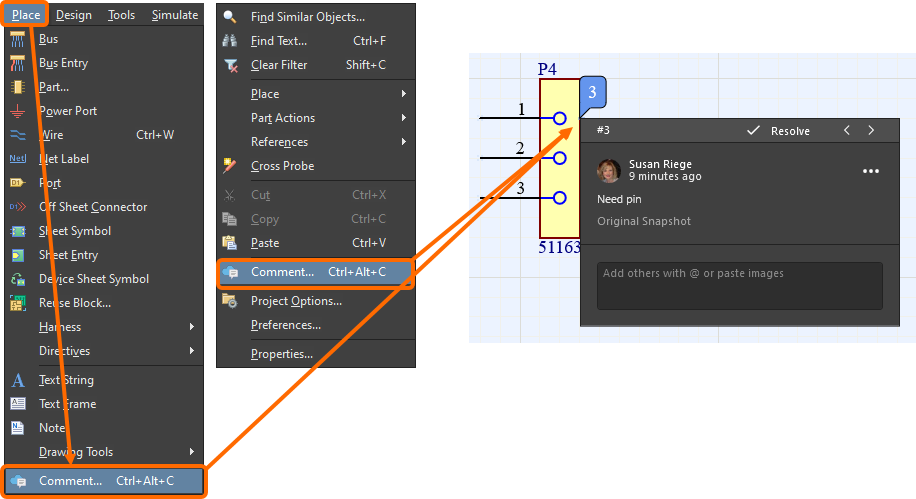

如需了解更多信息,请参阅 Creating a Manufacturing Drawing for a Harness Design 页面。 放置注释功能 在Wiring Diagram(*.WirDoc)和Layout Drawing(*.LdrDoc)中,添加了添加注释功能。注释是用户添加的说明,可以应用于文档上的点、对象或区域,并且可以由其他用户进行回复。可以使用Place菜单、右键单击上下文菜单、设计区右上角的 图标或快捷键Ctrl+Alt+C来完成注释放置。下图显示了在Layout Drawing中放置的注释。

图标或快捷键Ctrl+Alt+C来完成注释放置。下图显示了在Layout Drawing中放置的注释。

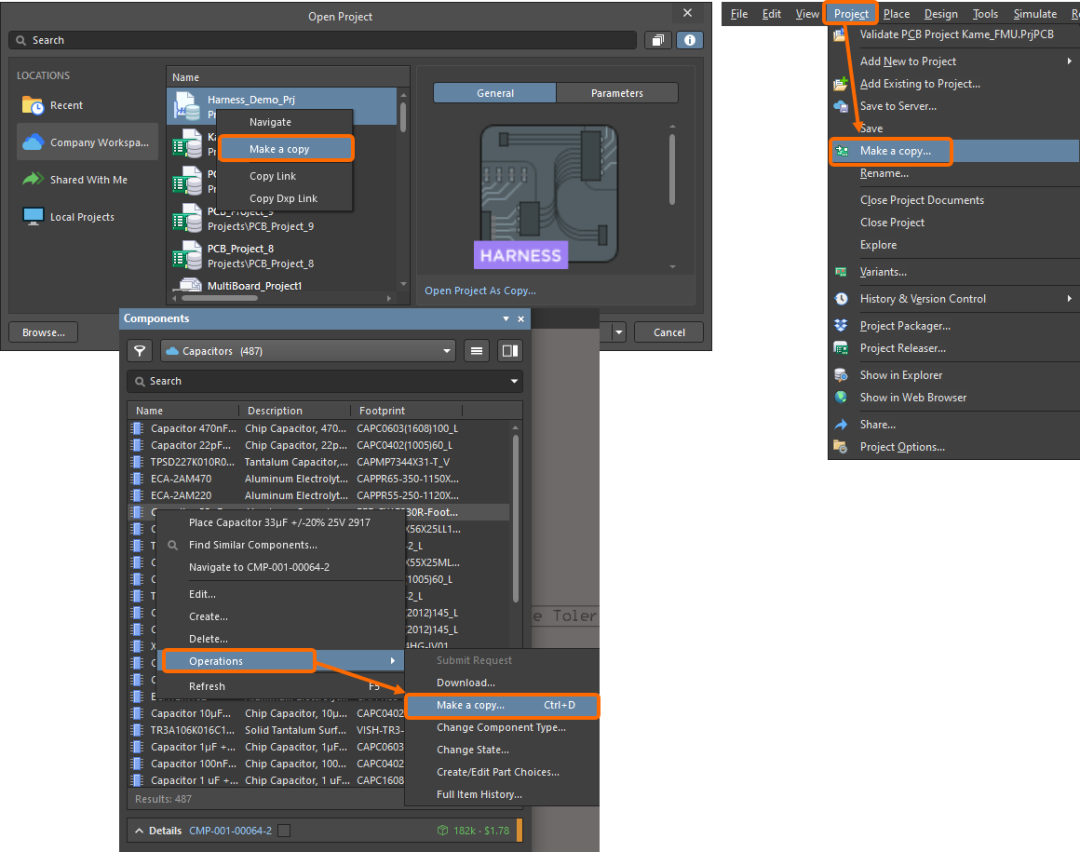

此功能将由Advanced Settings对话框中的Harness.Comments高级选项进行控制,并默认启用。 如需了解更多信息,请参阅Document Commenting页面。 数据管理改进 重命名了‘克隆’菜单命令 将Clone命令重命名为Make a Copy Throughout the UI,以阐明其功能。下图所示为几个位置的示例。

导入/导出改进 用于定义xDX Designer导入参数映射的选项 Mentor xDX Designer Import Wizard现在包含一些选项,允许您为Footprint、Designator、Comment和Description的元件映射定义替代参数。您可以将“;”用作分隔符,在文本框中列出多个参数,如下图所示。如果第一个参数不存在,则将按顺序使用下一个参数。

如需了解更多信息,请参阅Importing a Design from xDX Designer页面。 Altium Designer 24.7中完全公开的功能 以下功能现已在本次发布中正式公开:

以绝对值形式出现的焊盘转角半径/削角 - 自24.0版开始提供