时间:2023-10-07 09:46

人气:

作者:admin

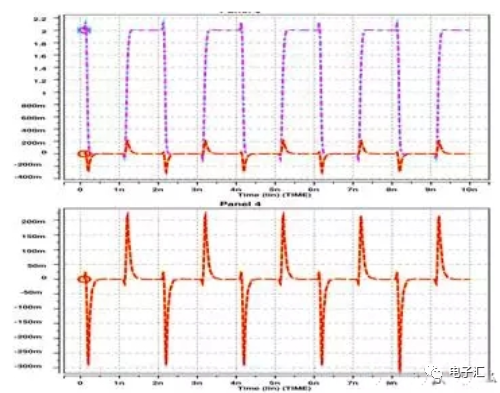

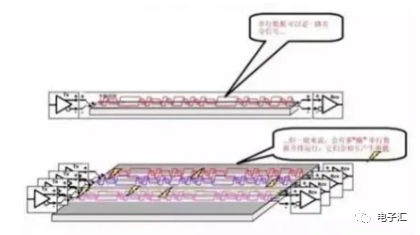

在射频电路研究学习的过程中,相信大家都遇到过在电路中信号频率的变高、边沿变陡、电路板的尺寸变小、布线的密度变大等问题,这些几乎是不可避免的问题。

这种影响信号完整性的问题叫做串扰,在电路计中普遍存在,有可能出现在芯片、PCB板、连接器、芯片封装和连接器电缆等器件上。如果串扰超过一定的限度就会引起电路的误触发,导致系统无法正常工作。

因此了解串扰问 题产生的机理并掌握解决串扰的设计方法,对于工程师来说是相当重要的,如果处理不好可能会严重影响整个电路的效果。

A、什么是串扰

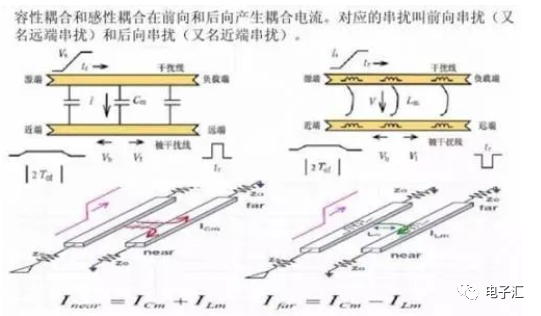

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

B、串扰是怎么引起的?

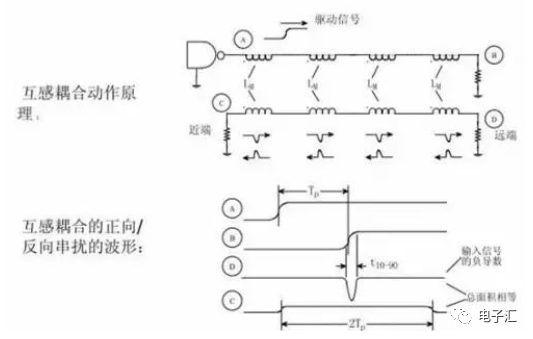

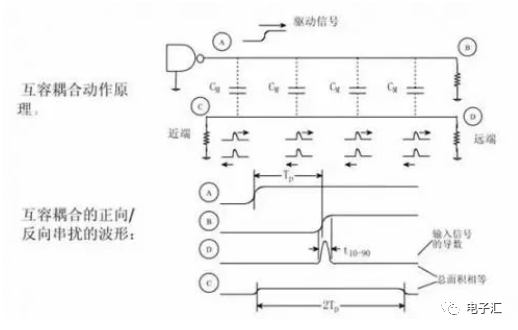

串扰是由电磁耦合引起的,耦合分为容性耦合和感性耦合两种。

串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生不期望的电压噪声。

容性耦合是由于干扰源(Aggressor)上的电压变化在被干扰对象(Victim)上引起感应电流从而导致的电磁干扰;而感性耦合则是由于干扰源上的电流变化产生的磁场在被干扰对象上引起感应电压从而导致的电磁干扰。

因此,信号通过一导体时会在相邻的导体上引起两类不同的噪声信号:容性耦合信号和感性耦合信号。

感性耦合:

容性耦合:

C、降低串扰有哪些方法?

当两个网络靠近时,一个网络的电流变化会引起另外一个网络的电流变化,即产生串扰。也就是两个网络之间的电磁场耦合产生。串扰只在上升、下降沿电流变化时产生。

降低串扰的方法有:

1、选择慢变化边沿信号的器件。

2、选择输出摆幅和电流小的器件。

3、为了减少PCB上的线间耦合,可以采取:

(1)加大电源地层与信号层间距;

(2)提高相邻信号层间距;

(3)减少并行走线长度;

(4)增加线间距抑制;

(5)地线隔离

(6)在受害线上采用匹配技术;

(7)关键信号线走STRIPLINE。

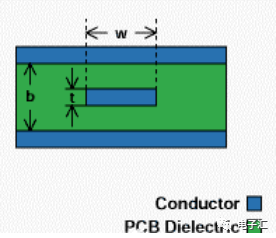

带状线:走在内层(stripline/double stripline),埋在PCB内部的带状走线,

如下图所示:

蓝色部分是导体,绿色部分是PCB的绝缘电介质,stripline是嵌在两层导体之间的带状导线。

因为stripline是嵌在两层导体之间,所以它的电场分布都在两个包它的导体(平面)之间,不会辐射出去能量,也不会受到外部的辐射干扰。但是由于它的周围全是电介质(介电常数比1大),所以信号在stripline 中的传输速度比在microstrip line中慢!

编辑:黄飞