时间:2023-09-21 16:30

人气:

作者:admin

1.1

什么是信号完整性

信号完整性是指在规定的时间内,信号从源端传输到接收端,信号不失真(能判断出信号的高低电平)。

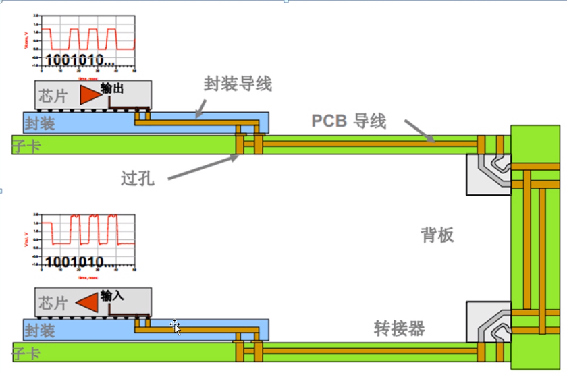

信号从源端发出以后,会经过传输线输送到接收端,期间必定会受到传输链路中各种因素的影响,例如电阻、电容、连接器、芯片封装等,这些因素会导致某些信号发生不同程度的形变,从而使接收端收到错误的信号电平,这些失真的信号就是所谓的信号完整性问题。

1.2

什么情况下要考虑信号完整性

早期时钟频率只有10MHz,对PCB的设计只需考虑如何把互连线拉通,因为对于低速信号,传输线本身的性能并不会影响系统的性能,所以不需要考虑信号完整性的问题,系统也能够稳定地工作。

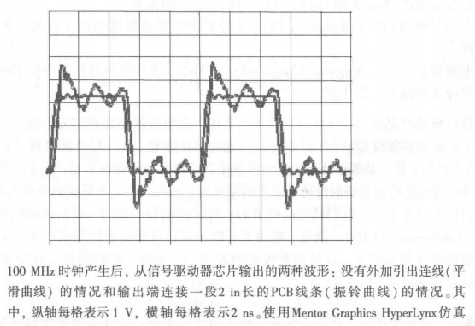

但随着科技的进步,现在的时钟频率越来越高,信号的上升边也变得越来越短。对于大多数电子产品而言,当时钟频率超过100MHz或信号的上升边小于1ns时,信号完整性就变得很重要了。通常将这种领域叫做高频/高速领域。

高速/高频信号:当信号的上升沿小于6倍的信号传输延时时,则被认为是高速信号。

考虑设计周期、成本、初版成功率等因素。

1.3

信号完整性需要研究的内容

信号完整性问题通常从这几个领域分析:

过冲、下冲、回沟、振铃、反射、衰减、串扰、阻抗突变、延时、损耗、地弹、抖动、误码率等等。

1.4

如何解决信号完整性问题

✦经验法则

工程师通过大量实验数据总结出来的经验,可以在设计之初作为参考,在进行问题查找的过程中也可作为一种判断标准。

例:

① 信号上升时间约是时钟周期的10%,即1/10x1/Fclock。例如100MHz时钟的上升时间大约是1ns。

② 直径为1MIL 的圆导线的局部电感约是25NH/IN 或1NH/MM。

✦仿真

利用电气仿真工具可用来预估互连线对信号行为造成的模拟效应。通过仿真,我们可以提前发现设计中存在的问题并提前规避。

✦测量

在制造产品之前,计算对于产品性能的预估起着关键作用,而测量技术则对减少风险起着关键作用。对任何计算结果的最终测试就是测量。

上一篇:如何正确的对PCB叠层进行构建