时间:2023-09-04 15:16

人气:

作者:admin

信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是接收器本身的特性。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间;而时钟边沿触发后,数据也必须保持一段时间,以便能够稳定读取,这就是器件需要的保持时间。如果数据信号在时钟边沿触发前后持续的时间分别超过建立时间和保持时间,那么这部分超过的分量分别称为建立时间裕量和保持时间裕量。

以常见的触发器为例来分析其基本时序参数:建立时间、保持时间和Tco,如图1所示。

图1 触发器时序图

在器件手册中可以查到每个器件的建立和保持时间参数,工程设计的目标是尽量提高建立时间裕量和保持时间裕量,以保证系统在外界环境发生有限改变的情况下正常工作。

传播延迟和飞行时间

信号在传输线上的传输延时称为传播延迟,它只和信号的传播速度和线长有关。飞行时间包括飞行时间和飞行时间,在Cadence SpecctraQuest软件中,将飞行时间称为终稳定延时,而将飞行时间称为早开关延时。

时钟抖动和时钟偏移

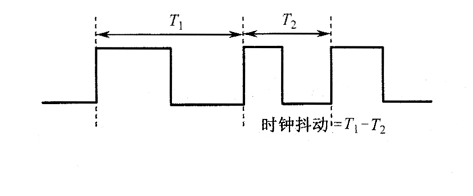

虽然系统时序设计中对时钟信号的要求非常严格,但实际中时钟信号往往不可能那么理想,常会出现抖动和偏移。时钟抖动是指两个时钟周期之间存在的差值,由时钟内部产生,与走线无关,如图2示。时钟偏移是指两个相同的系统时钟之间的偏移,包含时钟缓冲器的多个输出之间的偏移;也包含由于PCB走线的误差而造成的接收端和驱动端时钟信号之间的偏移。在时序设计中都需要考虑这些因素。

图2 时钟抖动

上一篇:电路板的可靠性设计

下一篇:PCB传输线的传播速度