时间:2022-07-14 16:36

人气:

作者:admin

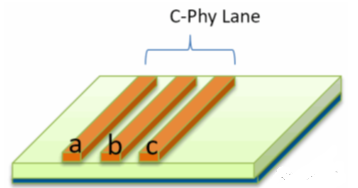

近年来,随着摄像和显示技术的快速发展,高清图像的像素逐年增加,无论是连接摄像头的软板,还是驱动主屏的主板,都慢慢地看到了MIPI C-Phy链路的设计身影。由于C-Phy大大简化了物理连接方式,所以C-Phy可以节省更多的PCB空间,为电子产品实现进一步小型化提供了可能性。C-Phy的基本协议信息如下:

高速时钟:嵌入式时钟

信道编码:特殊的状态编码减少时钟频率

最大传输速度:约17.1Gb/s

Lane最大速度:5.7Gb/s

最少管脚数量:3pins(TX) 1lane(TX)

最大管脚数量:9pins(TX) 3lane(TX)

在软件设计方面,目前还没有看到具有完美设计C-Phy链路的工具,通常还是要通过工程师来手动把控C-Phy链路设计,保证3条线之间的耦合,等长以及相位控制在容差范围之内,为设计带来了不小的难度,稍有不慎,就会造成传输速率提升不上去,甚至设计失败的风险。本文老吴为大家介绍如何基于Hyperlynx DRC实时自动地检查C-Phy链路设计的质量,为高清图像传输保驾护航!

工具:HyerlynxDRC VX.2.8

规则一:C-Phy 阻抗检查

检查目的:检查一个MIPI C-Phy的三个网络是否满足阻抗及差分阻抗值要求。

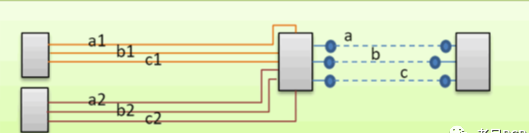

规则二:C-Phy 等长及过孔数量检查

检查目的:一个C-phy组中3个网络的长度必须满足容许误差要求,同时过孔数量必须相等。

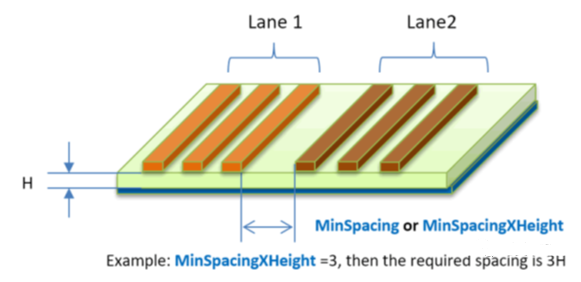

规则三:C-Phy 组之间检查

检查目的:为避免C-Phy组网络间的串扰,两个C-Phy组网络同层走线之间的间距必须满足最小间距要求。

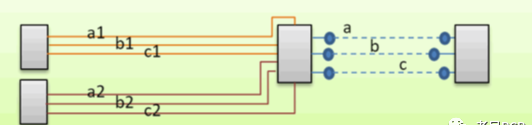

规则四:C-Phy 对称性检查

检查目的:检查一个MIPI C-Phy的三个网络是否走线对称。

无论您的PCB工具使用的是Xpediiton,PADS, 还是Allegro,以上4条检查项都可以在你设计过程中实时进行检查,当发现问题时及时定位或输出相应包括,大大节省了人工检查的时间成本以及为后续仿真减轻了压力。每一条规则都带有相应的参数信息,这里就不再一一展开为大家解释了,如果有需要的朋友,欢迎与老吴进行联系。

总结,MIPI CPHY在MIPI DPHY的基础上成倍增加了带宽,减少了线对数量,在高速大靶面传感器和高分高刷新移动设备OLED应用上越来越普及。Hyperlynx DRC基于目前软件条件,提供了自动化检测验证方案,为C-Phy设计提供了高效的验证平台。

上一篇:PCBA的拆焊方法介绍

下一篇:制作一个低成本的自动回流焊热板