时间:2020-04-09 21:28

人气:

作者:admin

(文章来源:深讲电磁兼容)

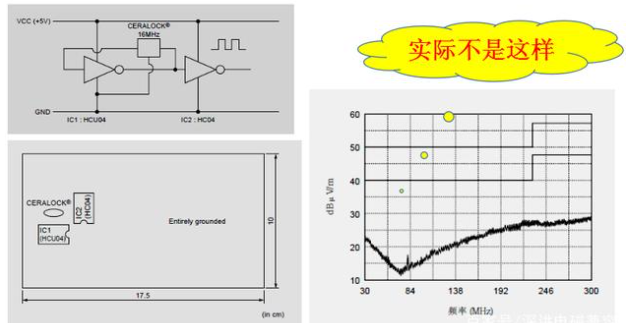

如图是我们设计的一个时钟发生测试电路,左下图是这个测试电路在印制线路板上的具体安装情况。右图是这个测试时钟电路的电磁辐射频谱图。从图中可以看出:这个时钟测试电路几乎没有什么电磁辐射。

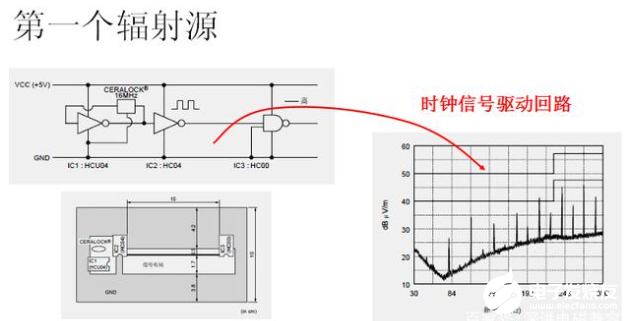

我们在前面的测试电路的基础上,在时钟电路的输出端连接了一个负载电路IC3,也就是一个与非门电路。

左下图是这个电路安装在印制电路板PCB上的具体布局情况,时钟电路的输出端同负载电路IC3与非门相距10公分。

右边图是这种电路布局情况下的电磁辐射频谱图。从右图可以看到,频谱图中电磁辐射明显增强了。这是因为,真正产生电磁辐射发射的并不是这些时钟、与非门等芯片,而是与时钟电路连接的导体,包括时钟信号线,电源线,地线等等,真正产生电磁辐射的是时钟信号线输出回路。

(责任编辑:fqj)

下一篇:PCB板选择性焊接的工艺流程解析