时间:2023-05-23 15:07

人气:

作者:admin

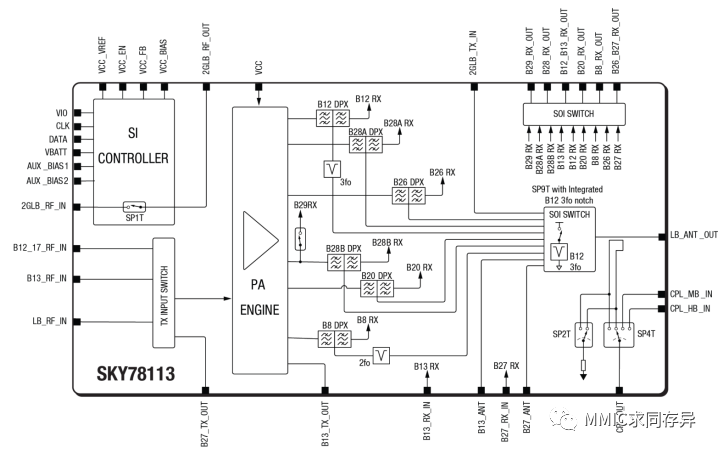

移动终端设备的射频前端模块(FEM)中射频开关处于关键位置且必不可少。射频开关的性能诸如插损、回损、隔离度、谐波抑制和功率容量等性能对射频前端链路的影响至关重要。

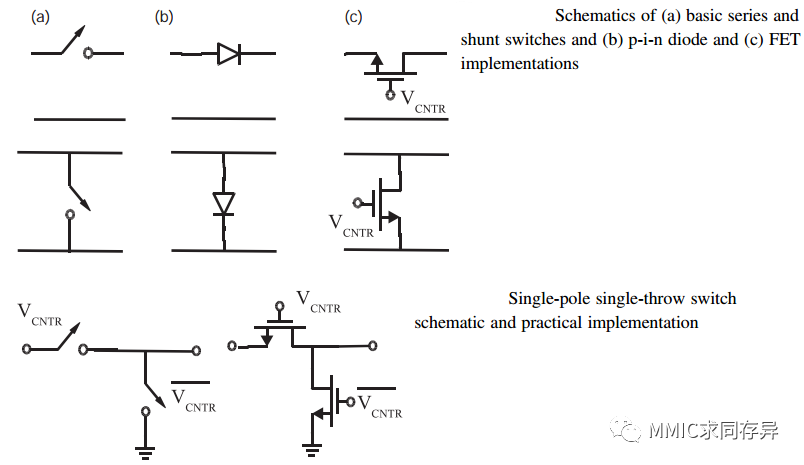

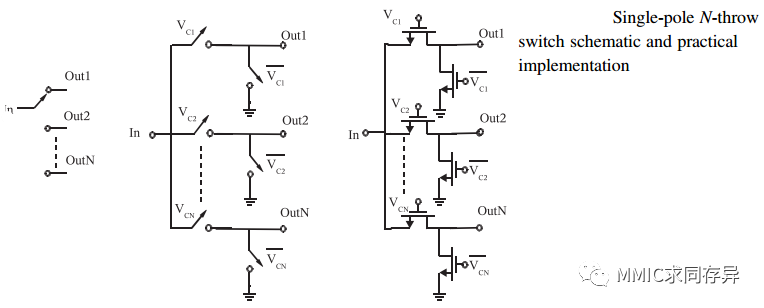

基本的串联、并联和FET开关可以简单图示,PIN二极管和肖特基(Schottky)二极管都可以用作开关。通过改变二极管的正反偏置条件可以实现二极管开关电路的切换。一方面,PIN二极管的Ron和Coff可以做的很小,便于实现很好的开关特性,但是,PIN二极管的偏置电源电压需要通过低通滤波器直接施加到RF信号端,PIN的集成也非常昂贵。相较于二极管,FET是三端口器件,不需要通过低通滤波器就可以将控制电压与信号路径隔离,可以将FET器件的源极和漏极之间用作开关,将控制电压加到栅极。开关的主要指标有插入损耗和隔离度等。

在时分多址系统中,射频开关用作切换天线到功放(上行)或者低噪放到天线(下行)通路。开关的插入损耗会增大接收通路的噪声系数,降低发射通路的功率附加效率。因此降低开关的插入损耗至关重要,此外,由于开关的上行链路需要通过较大的射频信号,一般还需要关注开关的P1dB和IIP3等线性指标。

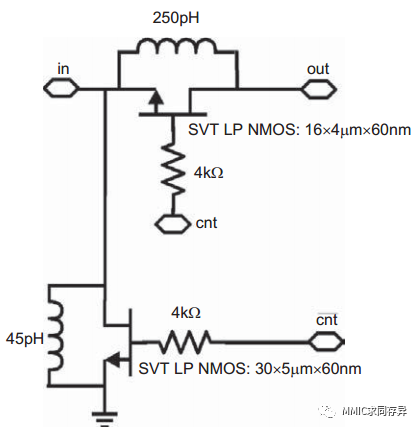

当FET开关关断时,开关的输出阻抗可以由Csw=Cdb + Cds + Cgd 并联一个大电阻表示。为了最大程度地提高高频下的截止阻抗,通常将一个电感与FET并联放置,以使其与输出电容Csw产生谐振,如下图并联系列天线开关所示。

我们注意到,与二极管开关不同,后者在导通时消耗偏置电流,而FET开关在“导通”或“截止”状态下均不消耗电流。但是,必须为开关中使用的FET的漏极和源极提供直流路径,以使其正常工作。如果不需要快速开关,通常会在栅极上串联几个kΩ的电阻,以减小漏极与地之间的电容。这种方案使栅极-漏极和栅极-源极电容串联出现,从而减少了输出电容的栅极-漏极分量,并改善了隔离和插入损耗。

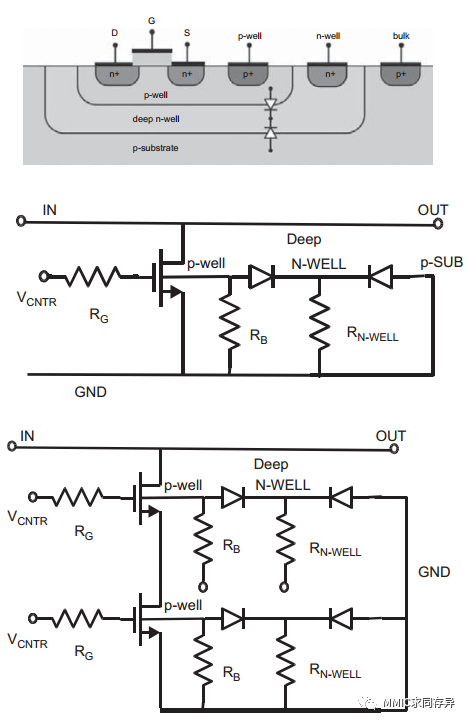

与SOI,蓝宝石硅(SOS)和III-V FET材料不同,硅MOSFET具有较大的漏极和源极电容,因此需要将开关放置在隔离的深n阱中并增加一个大电阻(一般为kΩ级)与衬底串联可以进一步减少损耗并改善隔离度,如下图所示。在所有FET开关中,可以通过垂直堆叠晶体管来提高线性度,但是会增大损耗。

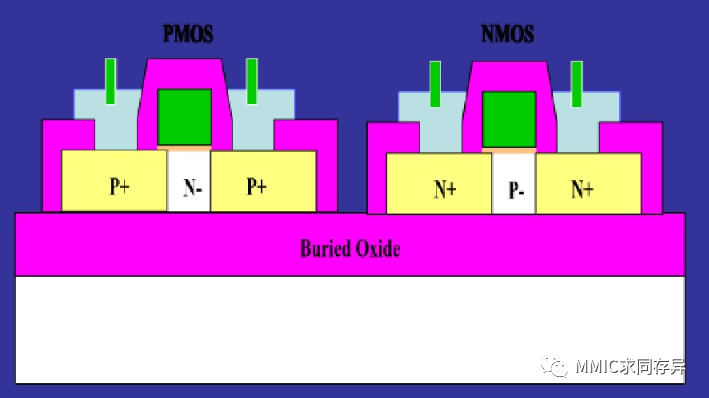

需要特别说明的是,目前射频开关设计采用的主要工艺是SOI和pHEMT。SOI是一种具有独特的Si/ 绝缘层/Si三层结构的新型硅基半导体材料。它通过绝缘埋层( 通常为SiO2) 实现了器件和衬底的全介质隔离,在器件性能上具有以下优点: