时间:2012-07-02 13:50

人气:

作者:admin

0 引言

随着人们对无线通信需求和质量的要求越来越高,无线通信设备的研发也变得越来越复杂,系统测试在整个设备研发过程中所占的比重也越来越大。为了更加方便地对所设计的系统进行调试和测试,无线信道模拟器是进行无线通信系统硬件测试不可或缺的仪器之一。目前,关于无线信道的模型研究比较多,而基于理论模型的硬件实现并不是很广泛,同时成品十分昂贵,所以利用FPGA实现无线信道模拟器变得很有意义,节约了成本,而且也便于实现。FPGA是在PLD的基础上发展起来的高性能可编程逻辑器件,使用FPGA进行数字逻辑设计,开发过程的投资较少,研制和开发的时间较短,并且因为引脚的可分配性电路一般比较简单,修改和优化比较方便,并且在实际中易于使用。同时由于FPGA并行运算的特点,在大规模的数字运算中很有优势,延时很小。

1 频率选择性衰落信道模型

多径传播信道的信道脉冲响应模式是模拟一个离散的广义平稳非相关散射模型(WSSUS)。这样的频率选择性衰落信道应该满足两个假设条件:

(1)在时间t(可能是几个码元长度)内,衰落的统计特性是平稳的;

(2)电波到达角和传播时延是统计独立变量。

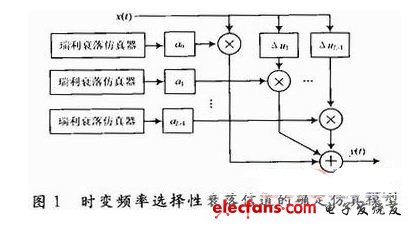

时变频率选择性衰落信道的确定仿真模型如图1所示。

Jakes在参考文献中介绍了一种单径衰落信道的仿真,且在此基础上提出了一种对频率选择性衰落信道的仿真方法。在原来第l径中的多普勒相移bnl的基础上,加上一个附加相移rnl,成为新的多普勒相移bnl+rnl,且保持其他参数不变。为了保证各个可分辨多径之间相互独立,所以必须选择合适的bnl和rnl,其中比较简单的一种方法是:

2 信道模拟器的FPGA设计

FPGA采用Xilinx公司的Virtex-2p,其中芯片工作时钟为100MHz。本文设置N0=8,fm=200 Hz,

为了计算方便,将所得的值扩大32倍,也就是左移5位之后四舍五入成整数值,存入寄存器调用。所以信道模拟器的实现过程主要为各个正弦波的FPGA实现,与对应的系数相乘叠加成单径衰落,输入信号经过l个路径时延之后叠加成为输出信号。

下一篇:怎样架构物联网云平台