时间:2025-08-28 09:34

人气:

作者:admin

在上期中,我们探讨了优化电能计量中隔离式电流检测的信号链成本和精度。

本期,为大家带来的是《使用混合热插拔架构防止高电流故障》,将讨论设计高电流输入电路保护具有哪些挑战,以及混合热插拔电路如何在任何故障情况下保护MOSFET。

引言

随着云的快速采用,以及物联网、人工智能和高性能边缘计算等技术趋势的出现,人们需要更快速、更灵活的企业系统来高效地管理工作负载。数据中心更高的数据吞吐量需要耗电量大的高速处理器,这将依靠典型 12V 电源轨的每台服务器的电流电平提高至 250A 以上,还需要 20 至 30mF 的负载电容,以满足系统的瞬态负载分布要求。

位于每台服务器前端的热插拔电路(结合使用热插拔控制器和金属氧化物半导体场效应晶体管 [MOSFET])可针对过载、输出短路等系统故障提供浪涌电流限制和保护。在系统故障期间,热插拔控制器可将MOSFET保持在饱和区域中,从而将故障电流限制在安全水平。但是,在设计可靠的热插拔电路时,这些与较大输出电容相关联的不断上升的系统电流却带来了巨大的挑战,因为MOSFET处理功率应力的能力有限。

本文讨论了设计高电流输入电路保护具有哪些挑战,以及将电子保险丝与常规热插拔控制器并联使用的混合热插拔电路如何在任何故障情况下保护MOSFET。

传统热插拔电路

简化的热插拔电路包含一个热插拔控制器、一个外部电流检测电阻器和一个功率 MOSFET。在系统故障期间,热插拔控制器会推动MOSFET在饱和区域中工作,以限制故障电流,导致MOSFET承受较大的漏源压降和很高的功率应力。

热插拔控制器通过可编程故障计时器 (TTIMER)实现功率限制方案 (PLIM),以提供 FET 安全工作区域 (SOA) 保护。选择适当的 PLIM和 TTIMER值非常重要,可用于确保所选的MOSFET在发生应力事件的最大工作温度下在其 SOA 限制内工作。如果所选的 FET 在设计中不可行,则您必须选择具有更高 SOA 的 FET,这让热插拔电路设计变得高度迭代且复杂。

电子保险丝具有集成的过热保护电路,可监测内部 FET 温度,并在 FET 承受较长时间应力时将其关断,从而确保 FET 在 SOA 限制内工作。目前电子保险丝器件只能在低电流下工作,因此,若要实现高电流电路保护,唯一的选择便是使用基于FET的外部热插拔解决方案。

设计大功率热插拔解决方案的挑战

为了确保 FET 一直处于其 SOA 范围内,热插拔控制器会实现一个功率限制方案,在 FET 的功率损耗达到 PLIM时触发故障计时器;如果功率损耗未降至 PLIM以下,则将在 TTIMER之后关断 FET。

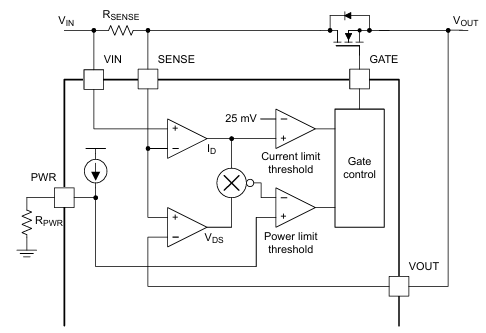

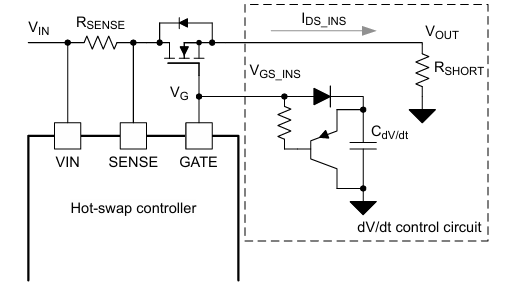

热插拔控制器的功率限制控制环路(如图 1 所示)包含一个电流检测放大器,用于监测检测电阻的电压 (VSNS),以获得电流信息,此外还包含一个电压检测电路,用于测量 FET 的电压。将电流检测放大器和电压检测电路的输出相乘,可以得到 FET 中的功率损耗。将该损耗值与和 PLIM成比例的电压进行比较后,您可以使用它来调节栅极电压。热插拔控制器可调节栅极电压,确保MOSFET中的功率损耗始终低于 PLIM。

图 1:热插拔控制器中的功率限制环路

虽然较低的功率限制设置可降低 FET 上的应力,但它也会减少热插拔控制器需要限制的电流量,因此电流检测放大器可以检测的 VSNS也会降低。VSNS较低会导致误差较大,因为理论上,电流检测放大器的失调电压会限制最小可能功率限制的设置。方程式 1 针对大多数热插拔控制器提供了建议最低检测电压 (VSNS-MIN):

方程式 1

其中,VSNS_CL是电流限制检测电压,VIN_MAX是最高输入电压,ILIM_CL是电流限制设置阈值。

高电流应用需要较高的电流限制阈值,因此必须设置更高的 PLIM,才能满足方程式 1 定义的 VSNS_MIN标准。PLIM升高后,需要更高的MOSFET SOA,最终导致难以找到合适的MOSFET来实现大功率设计。例如,12V、250A 的设计要求 FET 能够在 100°C 处理 560W 的功率应力,持续时间为 1ms,而现有的商用 FET 无法实现这一点。

驱动大容性负载的挑战

对于具有较大输出电容的设计,输出 (dv/dt) 控制电路可在启动期间处理 FET 功率应力。放置在栅极-GND 之间的电容器Cdv/dt可限制栅极和输出电压的压摆率,从而限制浪涌电流。

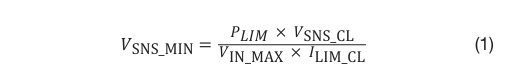

下图显示了带有输出 dv/dt 控制的典型启动波形。您必须设置足够低的压摆率和适当的Cdv/dt值,确保 MOSFET 保持在其 SOA 范围内。当 MOSFET 中的功率损耗降低且分布在较长的时间段内时,它们可以处理更多能量。因此,随着输出电容增加,您需要更高的Cdv/dt来降低 FET 在启动期间的浪涌电流和功率损耗。例如,要在 SOA 范围内运行特定 FET,10mF 的输出电容可能需要 47nF 的 Cdv/dt,而 30mF 的输出电容需要 330nF 的 Cdv/dt。

图 2:带有输出 dv/dt 控制的启动

启动至短路期间,热插拔控制器要求路径中流过一定量的电流(方程式 2 中的 IDS-INS),才能检测并触发功率限制故障。

方程式 2

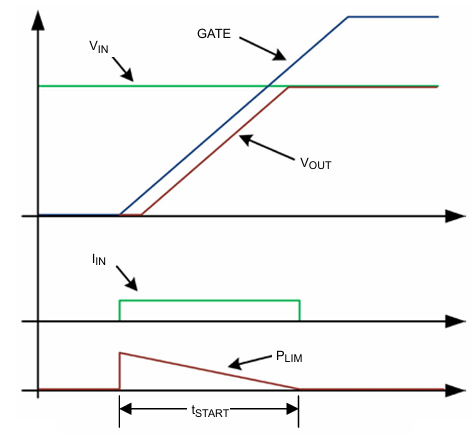

较大的 Cdv/dt会减慢栅极电压斜升速率,导致延迟达到建立 IDS-INS所需的栅极电压,从而增加故障检测时间,并致使MOSFET承受很大的 SOA 应力,尤其是当短路阻抗 (Rshort) 升高时,该阻抗由方程式 3 所定义,如图 3 所示:

方程式 3

图 3:高阻抗短路下的栅极电路

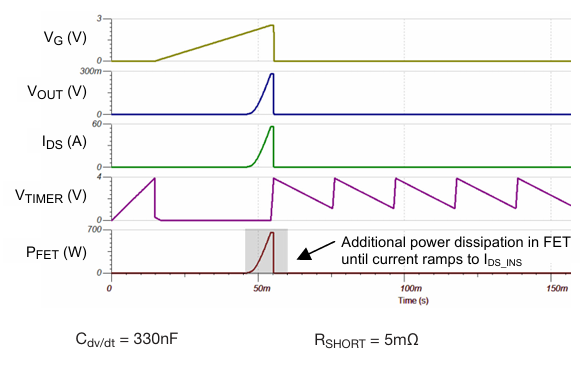

图 4:5mΩ 阻抗短路时 FET 上的功率应力

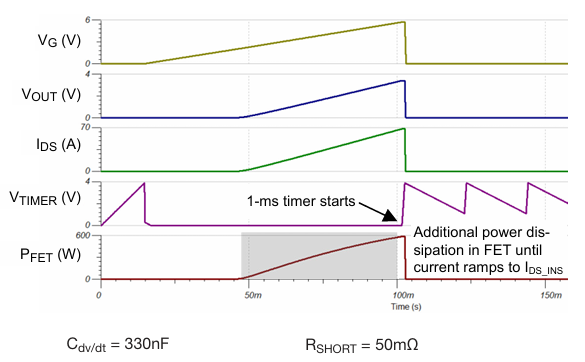

图 5:50mΩ 阻抗短路时 FET 上的功率应力

考虑一个包含两种不同阻抗的输出短路:5mΩ 和 50mΩ。如果在启动期间发生5mΩ 短路,随着栅极电压逐渐升高,短路电流会以更快的速度上升,短短 6ms 便会达到功率限制阈值(300W)。达到阈值后,将触发TTIMER并关断 FET。另一方面,50mΩ 短路阻抗会减慢短路电流的上升速度,热插拔控制器需要花费大约 50ms 来检测 300W 的功率限制阈值。该瓦数对应 15J 能量,这个巨大的能量可能会损坏FET,如图 5 所示。

混合热插拔解决方案

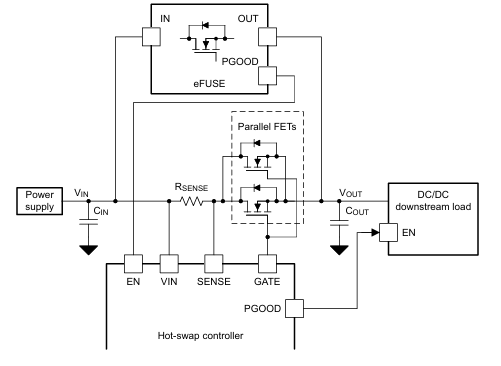

混合热插拔解决方案包含一个与传统热插拔电路并联的电子保险丝,如图 6 所示。在该电路中,电子保险丝将利用其集成的过热保护功能来应对高应力事件。

图 6:混合热插拔配置

电子保险丝的 PGOOD 信号连接到热插拔控制器的使能引脚,热插拔控制器的 PGOOD 信号则连接到下游负载的使能引脚。这些连接可确保:

•热插拔 FET仅在电子保险丝将大型输出电容器充电到接近输入电压后导通。FET 启动时两端电压几乎为零,从而在启动期间消除功率应力。

•下游负载仅在热插拔 FET 得到完全增强后启用,以便FET提供低阻抗路径(与电子保险丝相比)并共享大部分负载电流。

• 电子保险丝在所有故障情况下均承受功率应力,而热插拔 FET在任何情况下均不受应力影响。

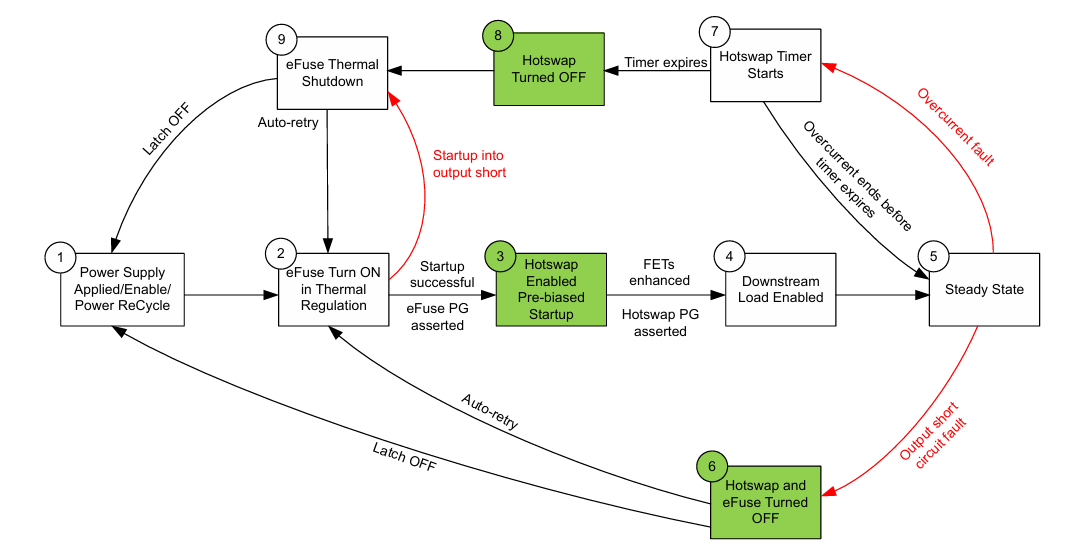

图 7 说明了启动期间和不同故障情况下的电路功能。状态 1 至 5 描述了启动期间的事件顺序,状态 6 至 9 则是不同故障情况的中间状态。

图 7:混合热插拔解决方案流程图

混合热插拔方案的主要优势是,热插拔 FET SOA 不再那么关键;您可以选择超低漏源导通电阻 (RDS(ON)) FET,它们通常更便宜,并且能大幅减少FET的数量。

重要的设计注意事项

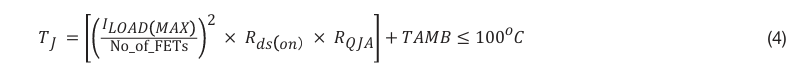

第一个设计注意事项是热插拔路径中并联FET的数量。我们建议让 FET 在稳定状态下运行,以便使结温低于 100°C。方程式 4 计算了给定负载电流下所需的并联 FET 数量:

方程式 4

其中,TJ是 FET 结温,ILOAD(MAX)是最大负载电流,Rds(on)是所选 FET 的最大 Rds(on),RQJA是 FET 的结至环境热阻。

接下来,选择电子保险丝。TPS1663 电子保险丝有集成的热调节环路,可在大容性负载下实现零噪声启动。

在稳定状态下,热插拔路径提供比电子保险丝路径更低的阻抗,因此能共享大部分负载电流。热插拔控制器还决定过流保护阈值,这与传统热插拔设计一样。应将此阈值设置为刚好超过最大负载电流。

对于电子保险丝,将电流限制设置为其最大值(TPS1663为 6A),以便在系统启动期间实现最快的输出电容器充电速度。

TTIMER对FET SOA来说不再关键,因为在混合热插拔架构中,热插拔 FET 不受任何应力影响。您可以仅根据负载瞬态要求选择故障计时器持续时间设置。

大功率设计使用多个并联 FET,但热插拔控制器的栅极驱动强度有限,这增加了 FET 的开通延迟时间。建议在开启下游负载时添加额外的延迟(5ms 范围内),以便为热插拔控制器提供足够的时间来完全增强FET。

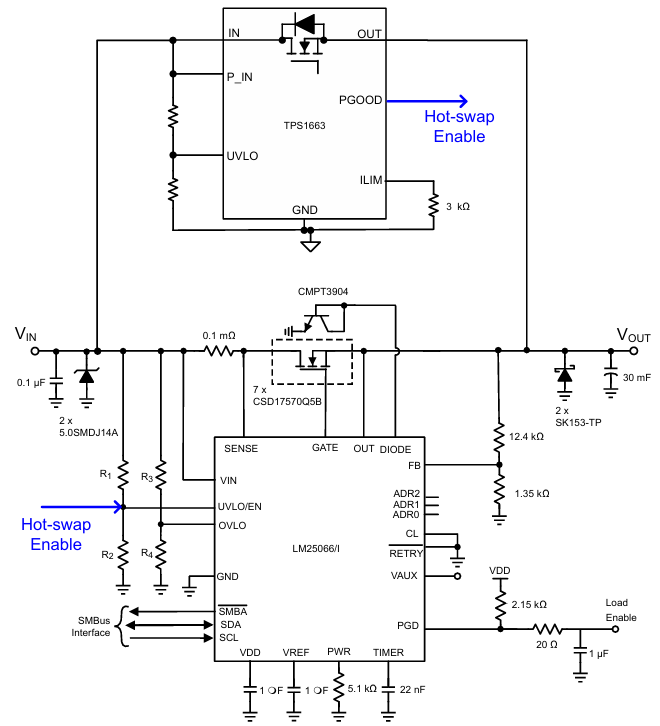

图 8 显示了一个使用LM25066 热插拔控制器和TPS1663 电子保险丝的示例混合热插拔电路,具有 12V 输入、250A 负载电流和 30mF 输出电容。

图 8:混合热插拔电路

测试结果

面向应力事件的混合热插拔解决方案使用LM25066 评估板和用于 TPS26633 和 TPS16630的评估模块,具有 30mF 输出电容器和 10A 热插拔电流限制,而且已经过验证。

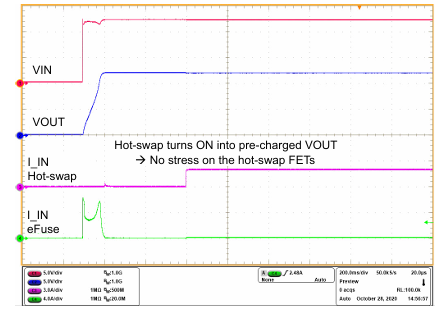

图 9 显示了该电路的启动和稳定状态行为。在启动期间,为输出电容器充电所需的整个电流会流经电子保险丝,此时热插拔路径尚未启用。启动阶段过后,几乎整个负载电流都会流经热插拔路径,因为它是低阻抗路径。

图 9:在 30mF 电容下启动

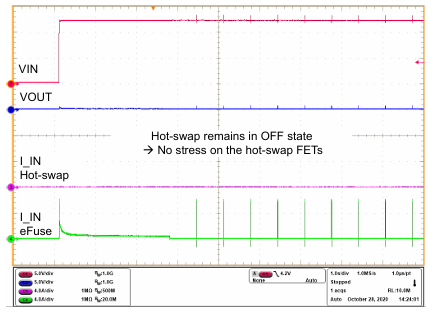

图 10 显示了输出端短路的电路的启动行为。电子保险丝在启动时进入热调节模式,并在热调节超时后关闭;每隔 650ms 持续不断地定期重试,直到输出故障消除。由于热插拔 FET 保持关闭,因此FET上没有应力。

图 10:启动至短路

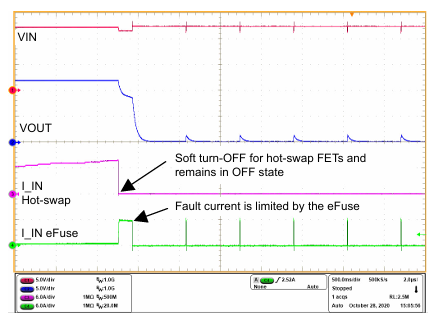

发生过载故障时,热插拔电路在关断FET前会产生过载电流,并持续计时器时间。图 11 显示了热插拔 FET 关断后,整个负载电流传输至电子保险丝路径,从而触发电流限制并最终触发热关断。

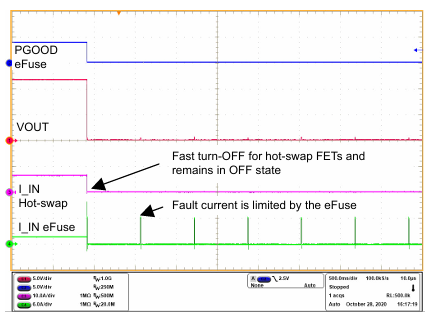

图 12 显示了在稳定状态下发生输出短路故障时的电路行为。热插拔和电子保险丝都立即关闭,以保护输入电源免受损坏。电子保险丝会持续不断地定期重试,热插拔 FET则保持关断,直到电子保险丝成功启动。

图 11:过载故障期间的电路响应

图 12:输出短路期间的电路响应

结论

由于服务器系统的功率级别持续增长,促使输入大容量电容提升到 20 至 30mF,以及 12V 电压轨下的满负载电流超过 200A。混合热插拔解决方案使用一个额外的并联电子保险丝,不仅解决了传统保护电路在较高功率级别下的难题,还消除了热插拔 FET SOA 方面的疑虑,从而简化了热插拔设计,并大幅降低了解决方案成本。混合热插拔解决方案针对不同的故障情况进行了测试,证明该电路可消除热插拔 FET上的应力。

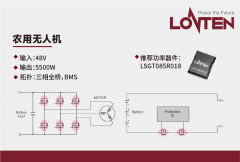

龙腾半导体SGT MOSFET LSGT085R018在智慧农业无