为什么引入寄存器模型

新需求:为带寄存器的DUT搭建UVM仿真环境

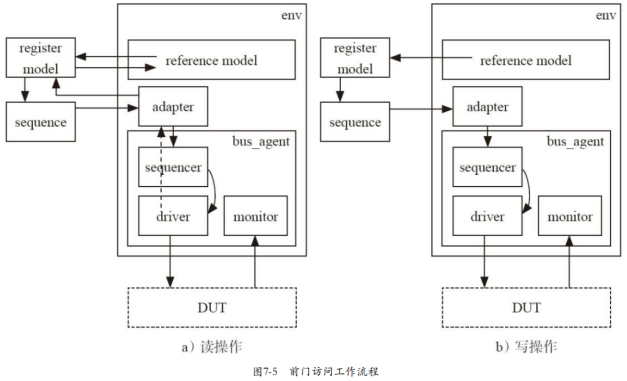

为了读写DUT中的寄存器:UVM提供了 配置寄存器的总线 (bus_agent=sqr+drv+mon)——前门访问DUT中的寄存器值

为了方便参考模型查看DUT中寄存器的值:UVM提供了 寄存器模型 ,作用如下

- 让前门访问操作更方便:将对DUT中寄存器的总线操作进行封装,通过寄存器模型这一暴露的接口可以方便实现对DUT的读写操作

- 新加入后门访问操作:通过层次化引用来读写DUT中寄存器的值(不消耗仿真时间),同样使用寄存器模型作为暴露的接口。

为DUT中的寄存器设定一个参考模型:引入UVM_PREDICT_DIRECT的predict操作,具体实现如下

- 在my_model中, 每得到一个新的transaction, 就先从寄存器模型中得到counter的期望值( 此时与镜像值一致) ,

- 之后将新的transaction的长度加到counter中,

- 最后使用predict函数将新的counter值更新到寄存器模型中。predict操作会更新镜像值和期望值。

- 在测试用例中, 仿真完成后可以检查DUT中counter的值是否与寄存器模型中的counter值一致

寄存器模型中的基本概念

- uvm_reg_field:寄存器的域,是一个uvm_reg中的一个字段/域

- uvm_reg:寄存器,至少包含一个uvm_reg_field

- uvm_mem:存储器,

- uvm_reg_file:引入后,uvm_reg配置时,其路径就不再需要uvm_reg_block的名字

- uvm_reg_block:包含uvm_reg或者其他uvm_reg_block(可设计层次化的寄存器模型)。一个寄存器模型中至少包含一个uvm_reg_block

- uvm_reg_map:存储所有寄存器的地址。每个reg_block内部, 至少有一个( 通常也只有一个) uvm_reg_map。

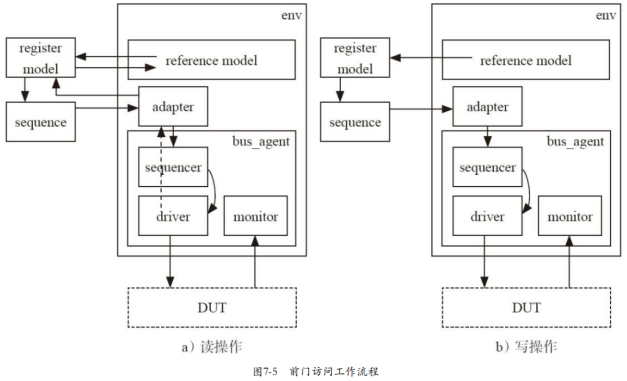

寄存器模型前门访问的实现

参考模型>寄存器模型>转换器>bus_sequencer>driver>dut>driver---

寄存器模型后门访问的实现

- 在reg_block中调用uvm_reg的configure函数时, 设置好寄存器的第三个路径参数(即后门访问路径:DUT内寄存器相对DUT顶层的路径,如:counter[31:16]表示dut中名为counter的寄存器的[31:16]位)

- 在将寄存器模型集成到验证平台时, 设置好DUT的根路径hdl_root(这样才能定位DUT在哪里)

- 在sequence中, 使用peek和poke任务 或者 UVM_BACKDOOR形式的read和write

寄存器模型中的期望值与镜像值

- 期望值:希望向此寄存器中写入的值——可作为DUT中寄存器的参考模型

- 镜像值:最大可能地与DUT保持同步

常用操作对期望值和镜像值的影响

- 针对DUT寄存器的read&write操作:用操作后DUT中寄存器的值更新 期望值和镜像值(会分前门/后门访问)

- 针对DUT寄存器的peek&poke操作:用操作后DUT中寄存器的值更新 期望值和镜像值 (只有后门)

- 针对期望值的get&set操作:更新期望值, 不更新DUT中寄存器,不更新镜像值

- update操作:用期望值 更新DUT中寄存器 和 镜像值

- mirror操作:用DUT中寄存器的值 更新 期望值和镜像值

- randomize操作:随机化 期望值,不随机化镜像值

- predict操作:

- 参数为UVM_PREDICT_READ和UVM_PREDICT_WRITE时:用操作后DUT中寄存器的值更新 期望值和镜像值——在read/peek和write/poke操作对DUT寄存器完成读写后自动调用

- 参数为UVM_PREDICT_DIRECT时:人为更新期望值和镜像值,不更新DUT中寄存器

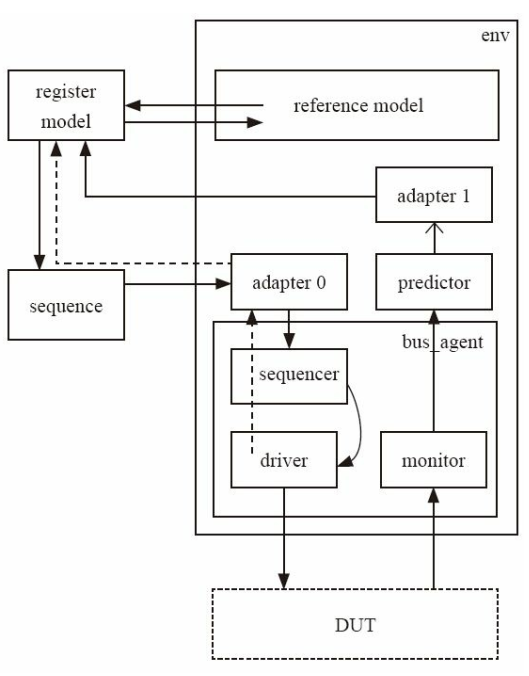

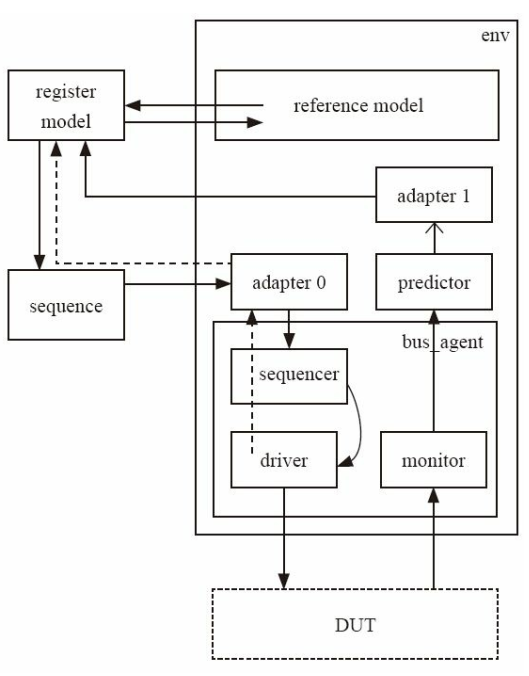

引入reg_predictor

引入reg_predictor的原因:配置寄存器的总线存在多个master时,可能存在 不通过寄存器模型 访问总线来配置DUT中寄存器的情况,这时 寄存器模型 就不能检查到 DUT中寄存器的变化 ,所以需要引入reg_predictor, 通过monitor检测总线,将采集到的tr发送给uvm_reg_perdictor 。如下图,

- 虚线为通过自动预测途径更新寄存器模型的路径。

- 实现为经由predictor更新寄存器模型的路径。