时间:2025-02-14 10:48

人气:

作者:admin

本文引入基于光学PCB的波导嵌入式系统(WES),用于AI/HPC数据中心,以克服CPO集成挑战。WES通过集成光学引擎与精确耦合结构,实现高密度、低损耗、无光纤的设备间光互连。

引入基于光学PCB的波导嵌入式系统(Waveguide Embedded System,WES),用于AI/HPC数据中心,能够克服CPO集成的挑战。WES通过集成的光学引擎和精确的耦合结构实现了高密度、低损耗、无光纤的设备到设备光学互连。

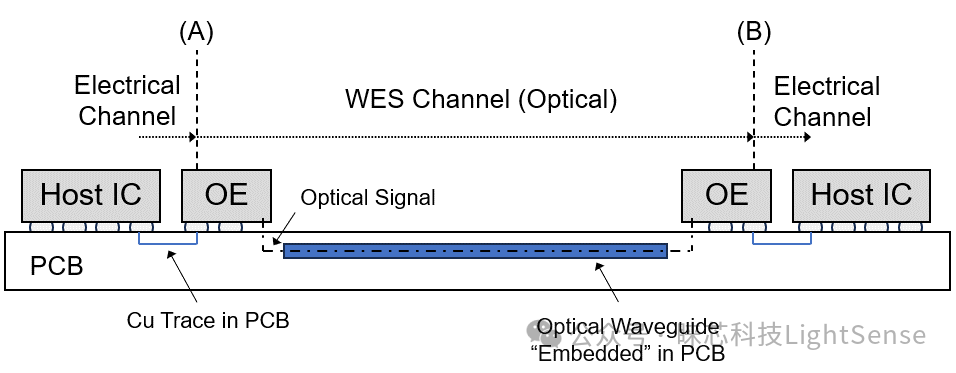

WES由三个关键组件组成,如图1所示:光学PCB、光学引擎和耦合结构。WES信道通过转换到光域并返回,使高速电信号能够从点(A)传递到点(B)。光信道通过半导体封装和PCB嵌入式波导形式的高度集成的光学引擎提供无缝的数据传输。

图1。波导嵌入式系统(Waveguide Embedded System,WES)的系统图。WES信道可以提供从PCB内的点(A)到(B)的高性能设备到设备的光链路。

A.光学引擎

WES信道的终端包括一个光学引擎(OE),它将电数据转换为光学数据,反之亦然。OE由Tx侧的VCSEL和驱动器IC以及Rx侧的PD和TIA组成,它们之间有一个短长度多模波导。

为了在PCB生态系统中实现无缝集成,OE必须具有与其他电气元件相似的外形尺寸。扇出晶圆级封装(FOWLP)是一种先进的半导体封装方法,是将VCSEL和PD与电子IC集成的最有前景的技术。LIPAC首次引入了光学系统级封装(O-SiP)技术,并为该项目提供了光学引擎。

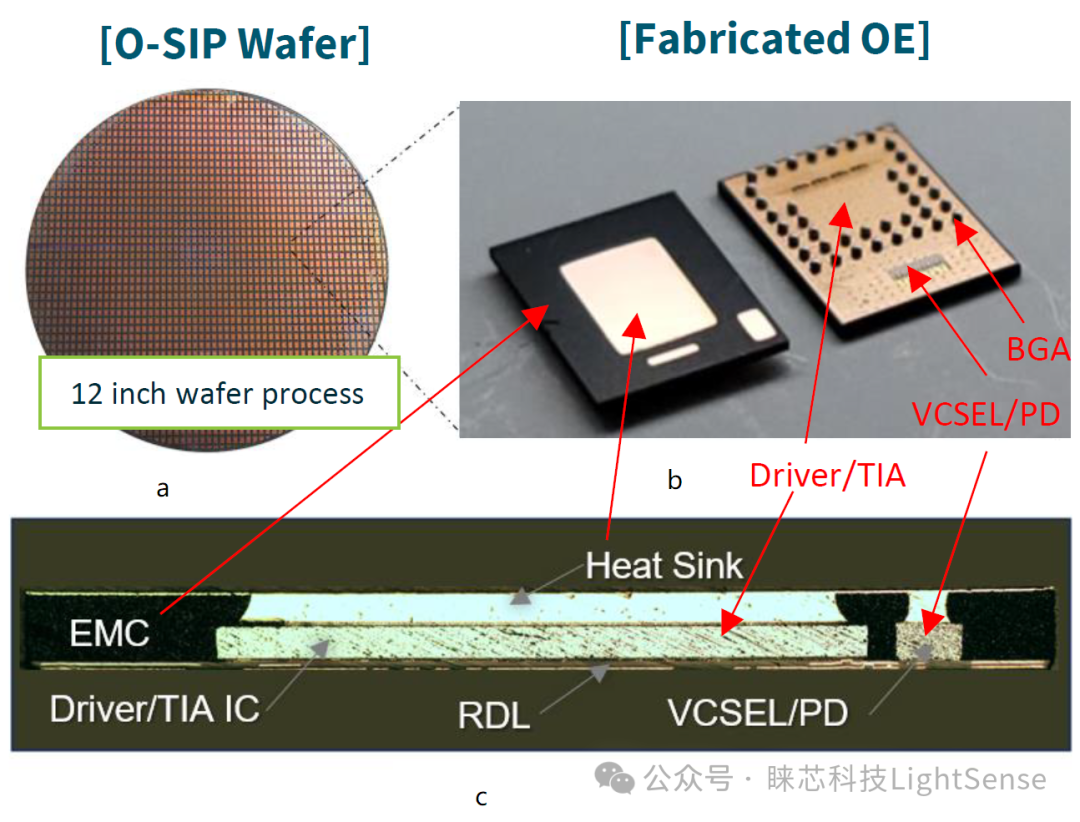

图2显示了基于FOLWP的OE,这是一种标准的BGA封装,但没有基板。OE既薄又小,可能适合未来物理信道密度的增加。光学窗口放置在封装的BGA侧,组装时面朝下,而封装的顶侧可用于散热。

图2。采用FOWLP方法制造的光学引擎。(a) 它可以以12英寸晶圆尺寸的格式生产。(b) WES光学引擎的前后两侧。在OE的背面可以看到球栅阵列和VCSEL/PD开口。(c) OE的横截面图。IC与VCSEL/PD在EMC材料内共同封装。OE中形成了作为RDL的精细电层。

B.光学PCB

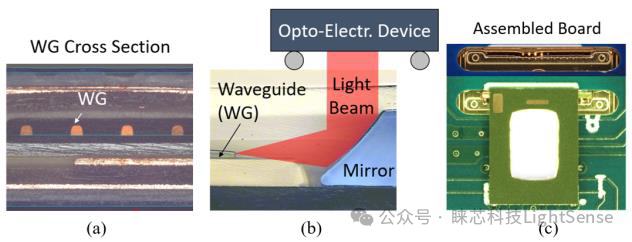

WES包括嵌入PCB中的多模波导,作为光学数据传输通道。与PCB中的铜迹线类似,光波导层可以布置为互连迹线,并且可以用聚合物基材料制造。波导的核心可以通过接触掩模光刻工艺或激光直接成像(LDI)制成,这两种工艺都与传统的PCB制造工艺兼容。10-40μm的包覆层用于夹持40-50μm的芯层,如图3(a)所示。

图3。(a) 带波导(WG)的O-PCB的横截面图。(b) O-PCB中OE和WG之间的光耦合结构。(c) O-PCB上带有OE和耦合镜的组装板图片。

最小弯曲半径通常约为15mm,而标准波导间距约为250μm。与电信道相比,这允许更高密度、更低损耗和更低串扰的光信道。

C.耦合结构

凹面镜分别用于从OE嵌入式VCSEL到Tx侧的波导和从波导到Rx侧的OE嵌入式PD的光耦合。如图3(b)所示,光束被聚焦到波导和PD中。耦合器在X-Y方向上的对准公差约为±15μm,Z方向为±40μm。反射镜组件具有与波导层中的基准配合的引导结构,允许反射镜组装到PCB上并与波导精确对齐。图3(c)显示了组装到PCB上的组装好的反射镜组件,该组件具有由各种光学元件制造的集成波导结构。其他形式的耦合器也是可能的。例如,microGlass提出了一种双芯片耦合结构(一个用于OE侧,另一个用于PCB侧)来提高对准精度。

演示器的组装

在PCB上组装OE需要比电气元件组装更高的精度。对准公差由耦合结构的光学设计决定。因此,应谨慎选择装配方法。在PoC演示器中,使用倒装芯片键合机将OE放置在PCB上,对准公差为±5μm。为了使用传统的IR回流方法,在放置OE之前,在PCB和OE之间涂上环氧树脂。环氧树脂固定了倒装芯片键合机提供的位置精度,并防止了红外回流过程中OE的移动。

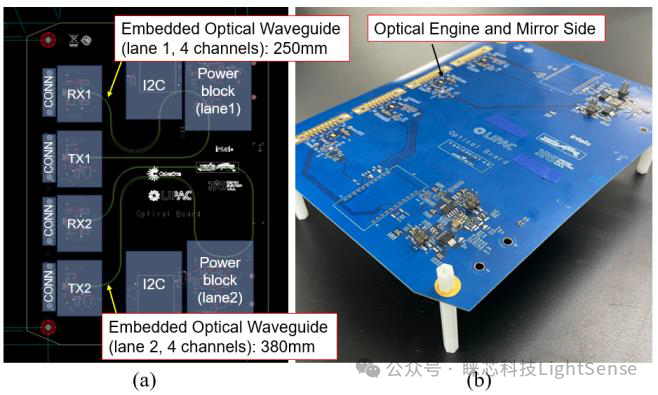

图4显示了PCIe演示器的OE和OPCB的设计和组装。它包括OE和高速同轴电缆连接器的操作电路,以测试射频性能。我们验证了VCSEL可以在这个系统中通电。波导损耗和耦合损耗加起来约为-6.5dB(最佳情况)。

图4。(a) 演示器的PCB设计,包括电源块、I2C电路、RF连接器。(b) 所有电气和光学部件均采用O-PCB制造。

上一篇:如何选择嵌入式主板厂家