时间:2023-10-08 14:53

人气:

作者:admin

CSR是控制状态寄存器,RISC-V中CSR寄存器,需要使用csrr、csrw、csrrw等特定指令进行访问。

M模式和S模式都有自己的CSR寄存器,但是大体上相同。下面列举一些常用的CSR。

mstatus

状态寄存器,保存了全局中断使能状态和其他状态,例如切换模式前,保存当前模式。

mtvec

异常入口基地址寄存器。保存发生异常时需要跳转的地址。

medeleg和mideleg

medeleg是异常委托,mideleg是中断委托。例如,在M模式下发生异常或中断时,可以通过这两个寄存器,将中断/异常交给S模式或者其他模式处理。

mip和mie

mie是中断使能寄存器,对需要使能的中断,在对应位使能。

mip是中断等待寄存器,表示目前正准备处理的中断。

hpm

全称Hardware Performance Monitor,硬件性能单元,用于性能计数。包括了两类寄存器:mhpmcounter和mhpmevent

mcounteren和mcountinhibit

这两个也是hpm相关的寄存器,主要用于控制hpm的使能、计数禁止。

mscratch

用于保存M模式指向hart上下文的指针,并在进入M模式的处理程序时,和用户寄存器交换。

mepc

发生中断时,当前程序的PC值,保存在mepc中,中断返回时,会从mepc读取PC值。

mcause

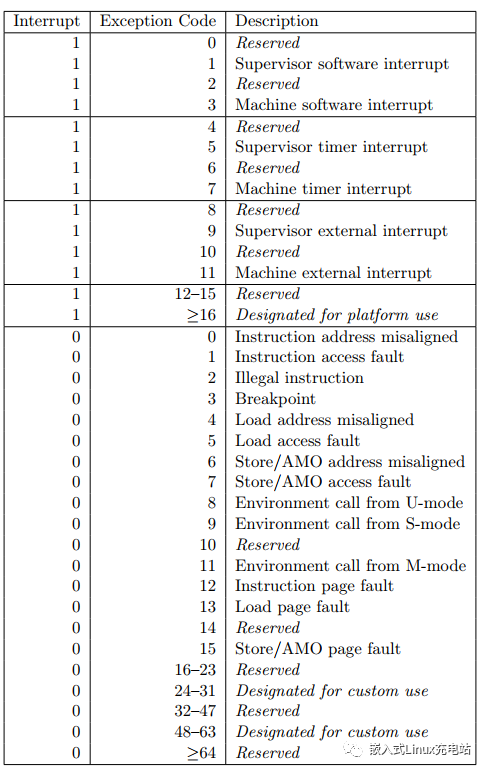

用于保存发生中断或异常的情况,中断和异常描述如下:

1代表中断,0代表异常,每个异常/中断都有对应的编码值,通过mcause的值,可以很清楚的知道发生了什么中断或异常,特别在调试过程,mcause发挥了很大作用。

mvtal

异常值寄存器,例如发生异常时,保存出错的地址。

S模式的CSR和M模式基本上是一样的,只不过将第一个字母m改为了s,例如mcause改为了scause,mvtal改为了svtal。它们的功能基本相同,这里就不再赘述了。

需要注意的是,S模式除了拥有M模式相同功能的CSR外,另外还增加了一个stap寄存器。

stap寄存器主要是给MMU使用,stap寄存器保存了页表的基地址,MMU通过stap可以找到第一级页表,进而找到物理地址。stap寄存器涉及到的内容比较多,关于stap相关内容,以后会详细展开讲讲。