时间:2023-07-07 11:27

人气:

作者:admin

今天我们要介绍的时序分析概念是 Critical Path 。全称是关键路径。刚接触后端的同学可能经常会听到这个概念,什么是Critical Path? 一般是指我们设计中时序最关键的路径,通常也就是timing最差或者最难修的路径。

实际工作中,leader或者同事也经常问你Critical Path在哪里。 这时,我们要学会从时序报告中去找到timing最差的path并去分析它。

那如何分析呢?下面提供几点建议

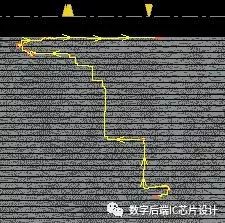

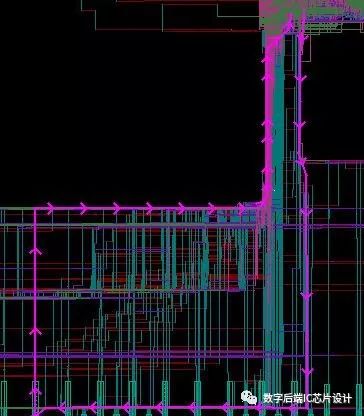

首先,我们可以看下这条path的走向是否合理,也叫作detour,通俗的解释就是有没有绕远路。

Innovus可以采用Global timing debug工具显示path path的路径

report_timing -machine_readable > critcal_path.mtarpt

ICC更加简单,可以直接在“ Import Path Pins ”里面黏贴timing path report显示

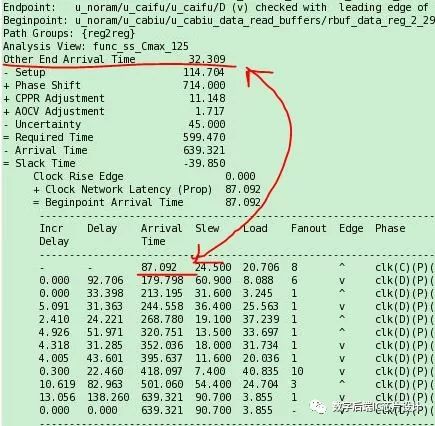

其次,我们可以看下设计的clock tree做得平不平。 通常来说,我们还是希望clock tree能尽可能做平一点,这样timing更容易meet。简单一点的方法,我们能直接从时序报告中得到clock tree的skew,就是自己算下launch clock path和capture clock path的delay差值(下图箭头差值),如果差值过大,那就要重点看一下clock tree的质量了。

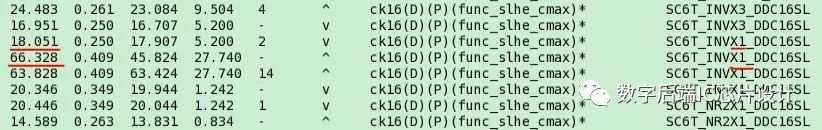

最后,我们也可以分析下具体data path上,有没有一些bad buffering, 过大的 load或者transition,甚至一些距离比较长的net都可以研究下。