时间:2023-06-15 10:51

人气:

作者:admin

写testbench最最核心的部分就是发激励,今天用一个简单的示例来介绍如何在uvm里给RTL发激励。

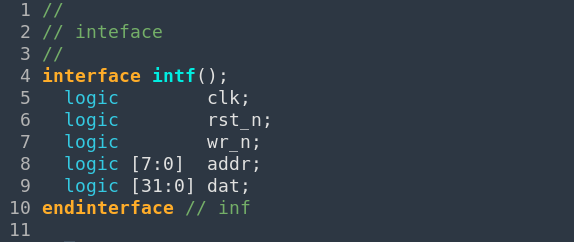

第一步,先来定义interface,如下。

interface是sv的一个关键字,级别等同于module,所以与module是并列的,一般单独写一个文件。

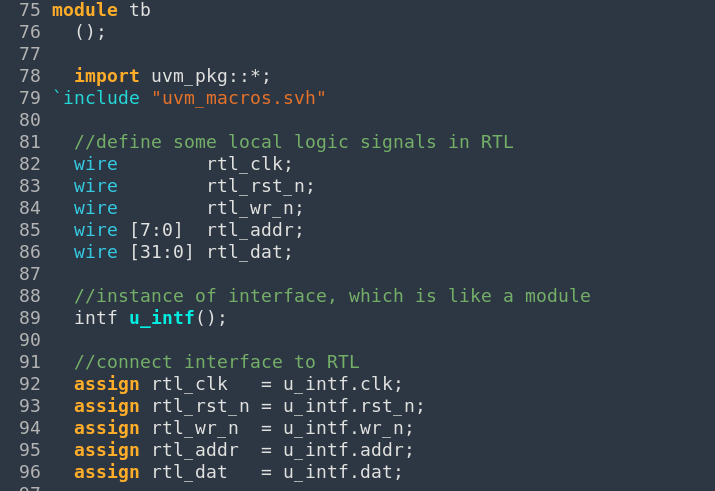

第二步,在testbench里实例化interface,并连接interface与RTL。

既然interface与module同级,实例化时就不能忘记括号。由于大部分信息不需要引到interface端口上,所以看上起来有点不太像模块例化。

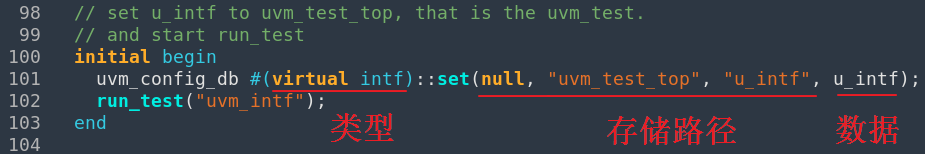

第三步,把interface实例化对象传递到uvm。

在run_test()之前,通过uvm里的函数uvm_config_db::set()函数把interface存储到指定的存储路径。

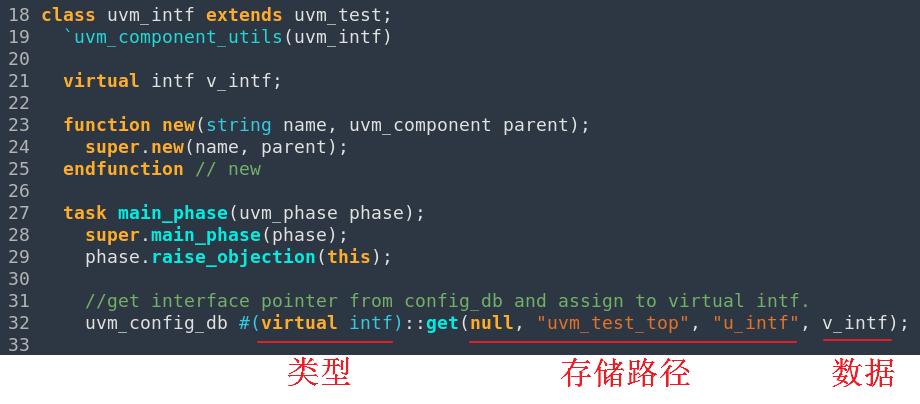

第四步,在uvm里读取interface,并存储到virtual interface里。

从名字上看,config_db是一种存储配置信息的数据库(类似全局变量,可以想象成一个关联数组),要正确存储和读取数据,需要类型和存储路径同时正确。v_intf有点像是一个指针,把读取的数据存到这个指针对应的存储空间里。

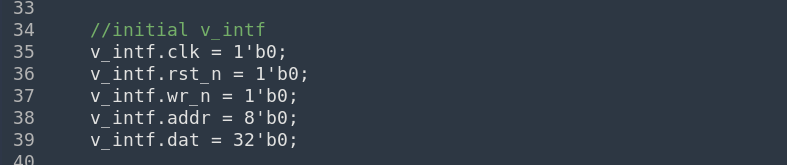

第五步,驱动v_intf的信号。

先初始化所有的信号。由于virtual interface指向了前面实例化的interface,给virtual interface赋值,等同于给真实的interface的信号赋值。

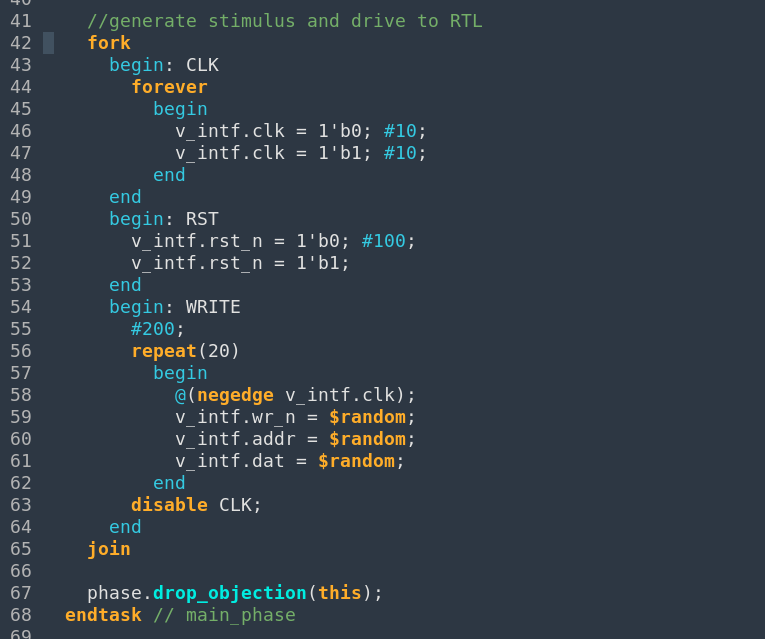

随机发一些激励,这部分与纯sv的写法没有差别。

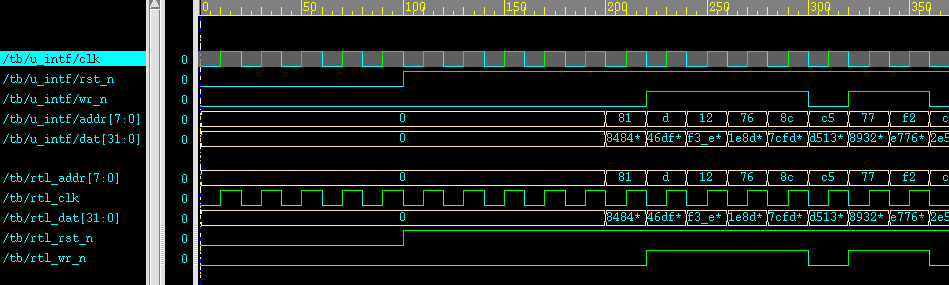

仿真结果