时间:2021-11-26 10:31

人气:

作者:admin

今天要介绍的时序分析概念是fanout。中文名是扇出。指的是指定pin或者port的输出端口数。

合理的选择fanout的数目对设计来说是非常重要的,fanout过大与过小都会对设计带来不利因素。

过大的fanout会使得驱动单元的负载过大,造成较大的延迟;过小的fanout会使得资源过于浪费,会使得path做得过长。

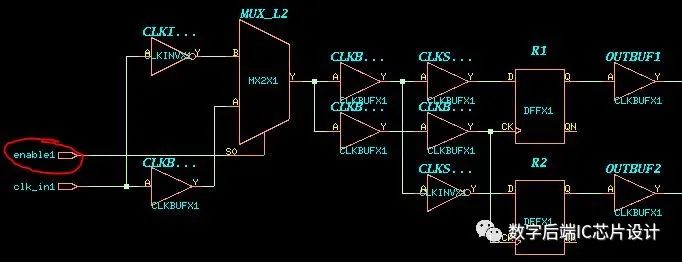

我们采用all_fanout来trace整个网表的扇出。但是需要注意的是all_fanout主要是时序路径上的连接,不一定完全是物理连接在一起。比如下图:

《CMD》all_fanout -from cppr_sub_2/enable1 -pin_level 3cppr_sub_2/enable1cppr_sub_2/MUX_L2/S0 cppr_sub_2/MUX_L2/Y cppr_sub_2/CLKBUF_L3_I1/Acppr_sub_2/CLKBUF_L3_I2/A

编辑:jq