时间:2020-10-18 11:02

人气:

作者:admin

(1)vip 简介

这里vip 就是video in port 的缩写,“VIP0 PortA”, “VIP0 PortB”, “VIP1 PortA”, “VIP1 PortB”,总共4个口

输入数据格式有yuv422i 和yuv420t 不小的这个i和t有啥区别 yuv420t/yuv420i,

输入数据位宽有“ 8-bit”, “16-bit”, “24-bit”

输入数据模式有

“Non-mux Embedded Sync”, “Line-mux Embedded Sync”,

“Pixel-mux Embedded Sync”, “Non-mux Discrete Sync”

example camerlink_drv.c:

char *gCameraLink_portName[] = {

“VIP0 PortA”, “VIP0 PortB”, “VIP1 PortA”, “VIP1 PortB”,

};

char *gCameraLink_ifName[] = {

“ 8-bit”, “16-bit”, “24-bit”,

};

char *gCameraLink_modeName[] = {

“Non-mux Embedded Sync”, “Line-mux Embedded Sync”,

“Pixel-mux Embedded Sync”, “Non-mux Discrete Sync”,

};

输入方式有hdmi ,sdi,vga, 输出有dvo0(vout1) dvo1(vout0) ,

(2)vip 电路图

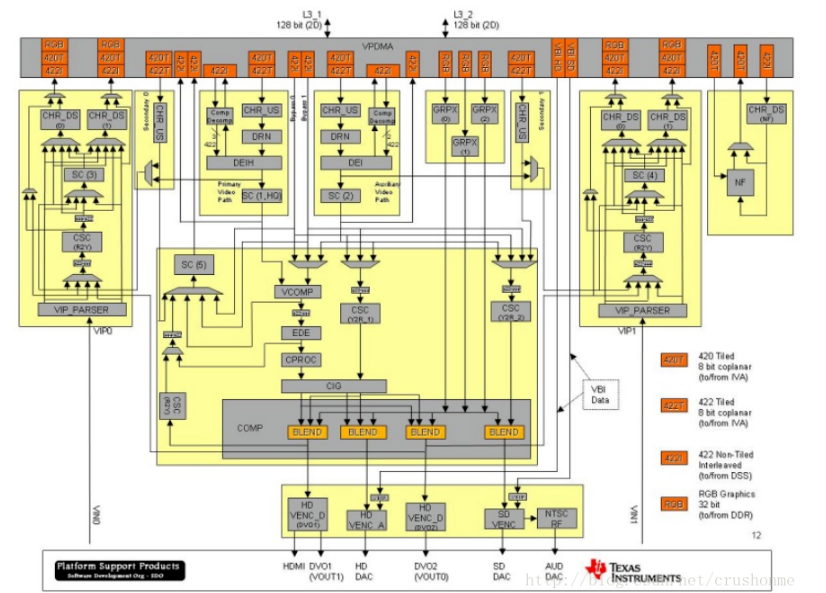

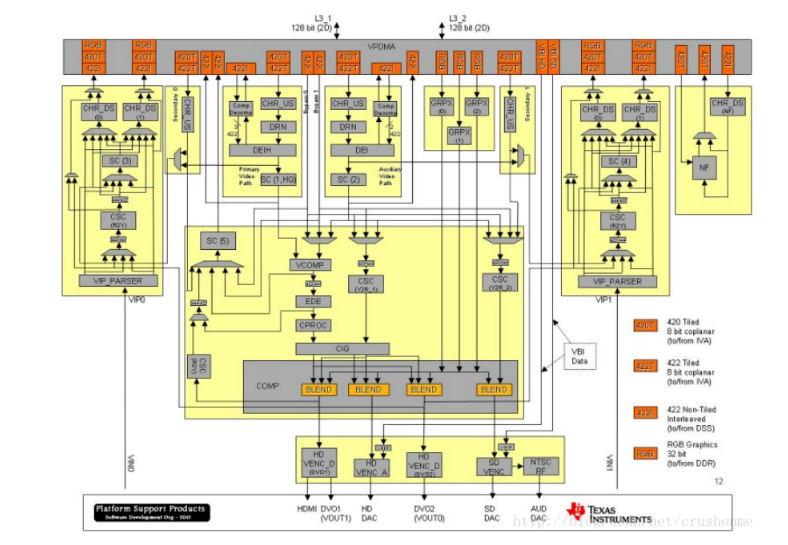

HDVPSS模块即High-Definition Video Process Sub System,主要用于视频的capture、deinterlacing、scaler、up/down sample、graphics、display等,由Media Controller Dula ARM Cortex-M3系统中的VPSS-M3控制。软件工程师在做程序的时候需要注意各个模块支持数据的输入格式和输出格式(另外需要注意的是:TI提供的RDK中限定了display controller的矩阵连接,如果希望灵活使用这个矩阵连接,需要自行拆分,关于该部分内容请参考HDVPSS_UserGuide.pdf中Display Controller Driver中Macro Mapping)。HDVPSS整体硬件框架如下图所示,注意数据格式。

播放输出:

播放接口:

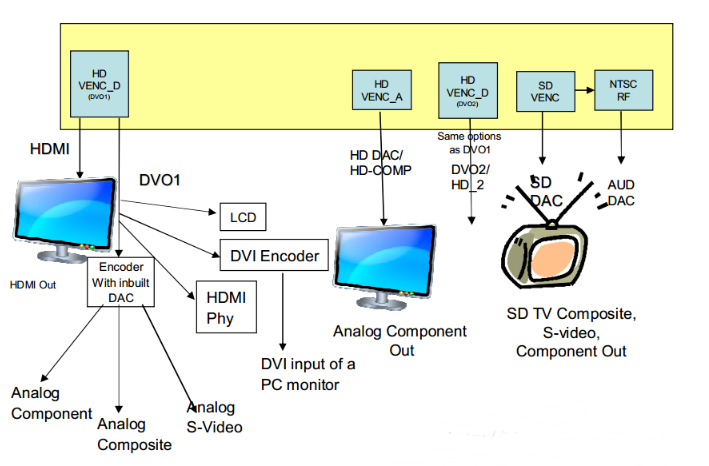

播放接口支持同时独立输出两路高清图像和一路标清图像,其中两路高清图像的源可以从两路数字接口(DVO1和DVO2,其中DVO1支持HDMI输出)和一路模拟接口(HDCOMP即内部集成的HD DAC)中选择,标清输出支持多种数据格式和多种视频制式。(需要注意的是DVO1与HDMI公用数字信号线,所以HDMI与DVO1输出是完全相同的,硬件工程师在设计的时候尤其需要注意。)

图1 播放口应用

DVO1:该接口的数据既可以直接输出数字信号也可以送给内部的HDMI Transfer Phy产生HDMI信号,可以支持10/20/30bit的内外同步数据输出,可以送出HS、VS、FID(Field ID)、AVID(Active Video ID)等时序信号。该接口有独立的时钟源,即hd_venc_d_clk。

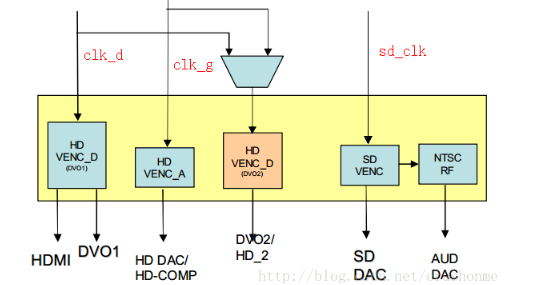

HDCOMP:该接口实际是内部集成的HD DAC输出接口,最高支持1080P60,像素时钟为148.5MHz,其时序参数是可编程的,具体请参考hdvpss中源码。HD DAC也有独立的时钟源,即hd_venc_g_clk。需要注意的是该接口支持VBI输出。

DVO2:该接口特性基本和DVO1相同,需要注意的是DVO2口没有独立的时钟源,其时钟源既可以共享DVO1的时钟源,也可以共享HD DAC的时钟源,因此决定了播放接口只能送出两路独立的高清图像(主要体现在分辨率上)。(注:在RDK中DM814x的DVO2的时钟源绑定到了HDMI口,如果希望HDMI和DVO2口同时输出不同分辨率的内容,请注意修改该部分内容,E2E上已经有很多人问道该问题。具体修改,请参照VPSS M3侧Display controller配置部分代码)

SD DAC:该接口支持PAL、NTSC、SECAM等标清视频制式,输出格式也是多种多样,包括复合信号(CVBS)、S端子、分量信号(YPbPr)、Euro-SCART(RGB)等。和HD DAC一样,该接口也支持VBI输出。

图2 播放口时钟分配

(3)vip 更换采集相机输入

同步:分为内同步和外同步

“Non-mux Embedded Sync”, “Line-mux Embedded Sync”,

“Pixel-mux Embedded Sync”, “Non-mux Discrete Sync”

注意:

对于Multi Channel模式,由于无法共用参考时钟,因此必须使用内同步模式,具体格式可以参考BT656格式。Single Channel支持三种数据格式,即:YUV444、YUV422、RGB888;Multi Channel仅支持YUV422格式。

采集口支持VBI数据采集;

对于Multi Channel模式采集,采集口内置了De-Multiplexing模块,该模块不需要CPU的参与;

采集口像素始终最高能达到150MHz,即Single Channel模式下采集分辨率可以达到1080P60,Multi Channel模式下采集分辨率可以达到16 Channel D1@30fps;

采集模块中内置RGB2YUV和YUV2RGB色彩空间转换模块(CSC:ColorSpace Conversion)、Scalar模块(缩放范围:1/8x ---8x)、降采样模块(YUV422toYUV420);

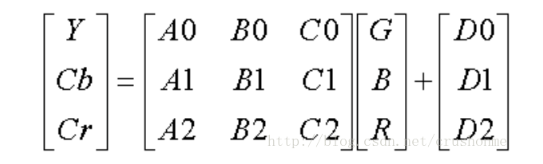

内置CSC模块矩阵系数 Ai/Bi/Ci 和偏置 Di 均可以设置,如下图所示。

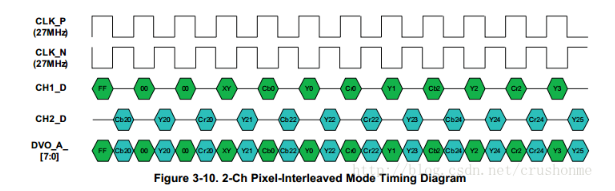

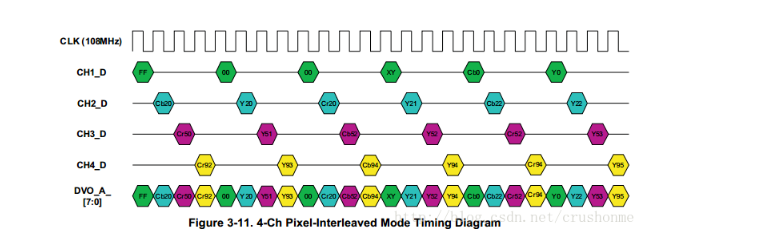

Pixel Mux:在DM8168的TRM和TVP5158的数据手册中都有详细描述,说白了其实就是一种利用时分复用的减少数据引脚数的方法,下面用两张图(均摘自TVP5158数据手册)来说明,分别是两路视频信号和四路视频信号(内同步格式,嵌入了同步信号,请参考BT656格式)的复用模式:

注:上图中时钟好像有点错误,两路D1的pixel mux模式下时钟应该为54MHz。

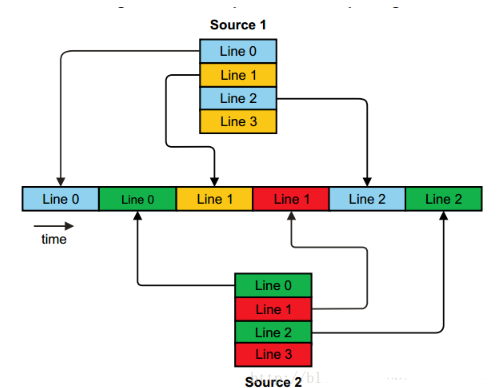

Line Mux:下图(截图来自DM8168 TRM)中是两路视频信号的line mux模式。

编辑:hfy