时间:2023-05-25 11:28

人气:

作者:admin

Part 01

今天听了下公司analog designer的介绍课程,有一些LVDS在信号上的观点非常亮,我做了点笔记,跟大家分享一下。

知识点:

1 LVDS多根bus,导致EMI大,叠加效应。

2 展频(SSC)可以展宽EMI测试图的凸起来的 尖峰 。

3 TX振幅缩小可以 减小EMI尖峰幅度 。调整LVDS边沿slew-rate,变缓。

4 slew调不好,PN错开,common mode noise会增大。频率是2倍(出现的周期,非信号带宽), rising错开一次,falling 错开一次 。

5 LVDS多根bus的每个bit 敲出去的时刻稍微做 偏斜 ,防止在同一时刻TX出去。做每根LVDS phase上的调整,能够有效降低EMI。

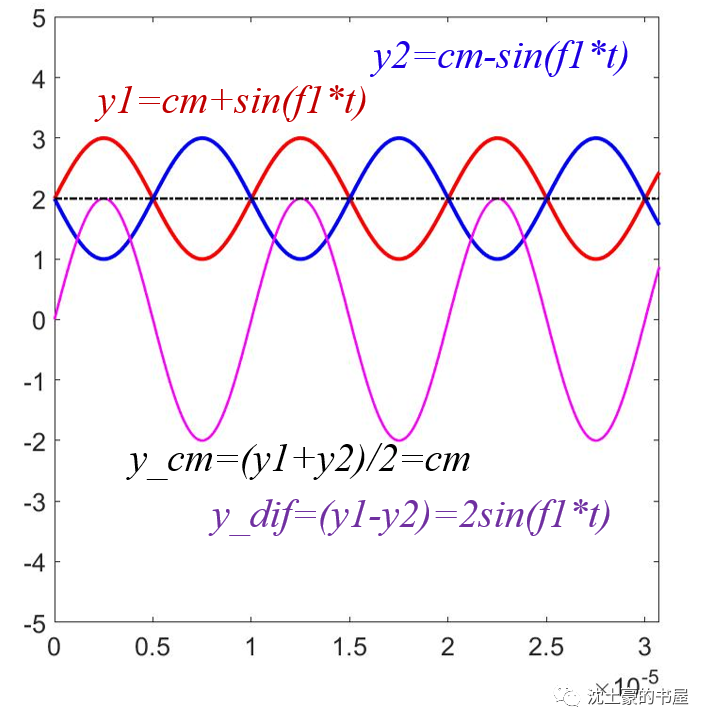

第4个观点,如果serdes PN完全对称,应该长下图那样。

y_cm是共模电压。y_dif是差分电压。

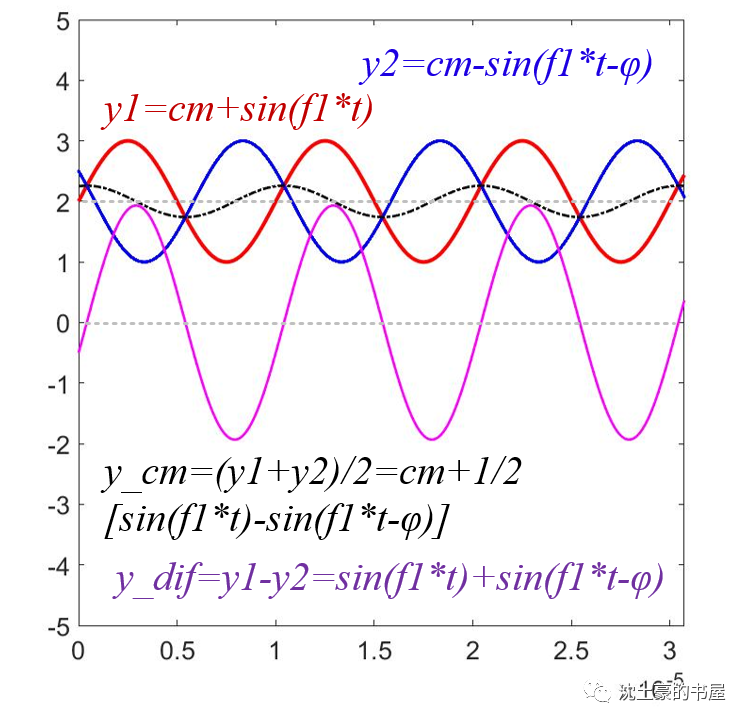

如果PN不对称,我在y2加了一个相位φ,黑色的y_cm是共模电压明显有了起伏。

因为每个码元有上升沿和下降沿,这个noise出现的频率将会 变成2倍 。

第5个观点也非常美妙,LVDS bus根数太多了,叠加效应导致EMI大,理论上LVDS要对齐每个bus的码元TX时刻,但是如果每个bit稍微有一点点phase 差异(不影响时序),EMI就会缩小。

Part 02

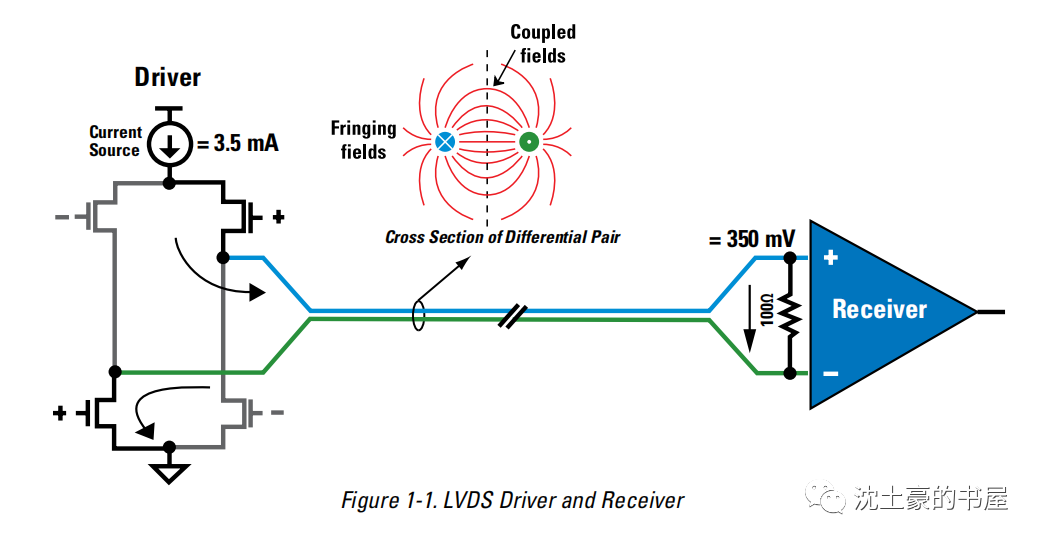

稍微介绍下LVDS,我也没有用过也不清楚,只知道有些ADC用,笔记本屏幕用。

LVDS的接口,应当也是serdes,通常会有很多根,时序上是对齐的。

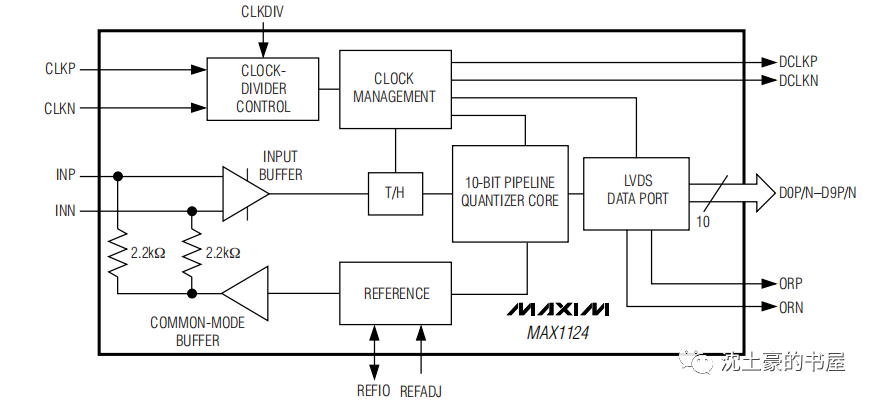

比如这颗ADC接口,D0P/N ~D9P/N,10组差分对,共同传信号。

上一篇:解决CAN总线干扰的三种方法